플래시 기반 임계 로직 셀로 구현하는 포스트‑팩터리 가중치 프로그래밍

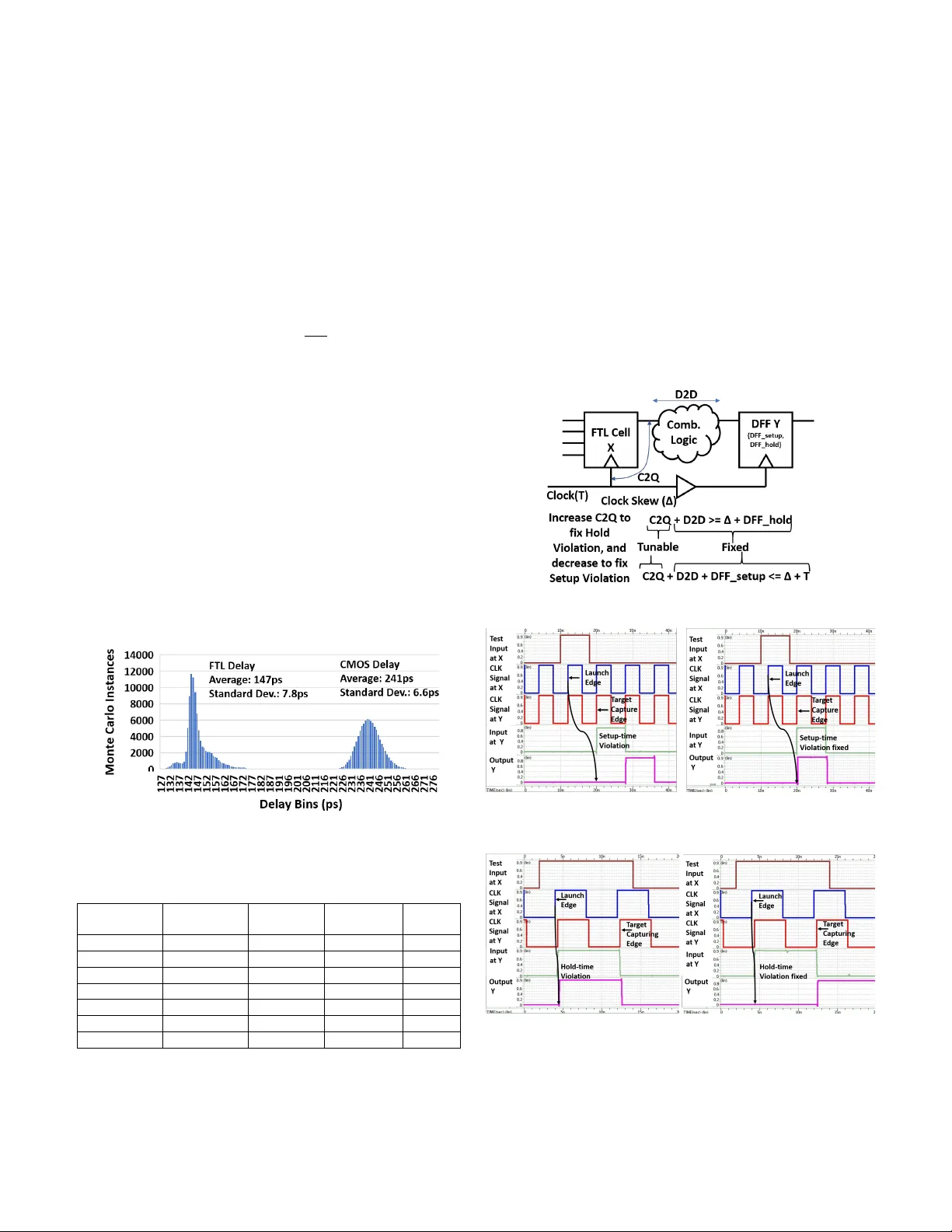

플래시 트랜지스터의 임계전압을 가중치로 활용한 임계 로직(FTL) 셀을 설계하고, 수정된 퍼셉트론 학습 알고리즘으로 포스트‑팩터리 프로그래밍 방법을 제시한다. 40 nm 공정에서 레이아웃 추출 파라시틱을 포함한 시뮬레이션 결과, 기존 CMOS 구현 대비 면적 79.7 %, 전력 61.1 %, 지연 42.5 % 개선을 보였으며, 몬테카를로 분석을 통해 공정 변동에 강인한 설계가 가능함을 입증한다. 또한, IP 보호, 타이밍 오류 보정, 노화 보정…

저자: Ankit Wagle, Gian Singh, Jinghua Yang

본 논문은 플래시(부동 게이트) 트랜지스터를 이용해 가중치를 물리적인 임계전압(Vt)으로 구현하는 ‘플래시 임계 로직(FTL)’ 셀을 제안한다. 기존 정적 CMOS 기반 임계 게이트는 다수의 트랜지스터와 복잡한 배선을 필요로 하여 면적·전력·지연 측면에서 비효율적이었다. FTL 셀은 입력 네트워크(LIN, RIN) 각각에 플래시 트랜지스터를 직렬로 배치하고, 두 네트워크의 전도도 차이를 차동식 센스 앰프와 SR 래치를 통해 비교함으로써, Σw_i x_i ≥ T 형태의 임계 함수를 전류 비교 회로로 변환한다. 여기서 플래시 트랜지스터의 Vt가 낮을수록 전도도가 높아져 큰 가중치를 의미한다.

FTL 셀은 세 가지 동작 모드를 갖는다. 1) **정상 모드**에서는 Vt가 사전에 설정된 상태에서 입력에 따라 LIN과 RIN이 전류를 공급하고, 센스 앰프가 차이를 판단해 래치를 제어한다. 2) **프로그래밍 모드**에서는 고전압(≈20 V) 펄스를 플래시 트랜지스터 게이트에 인가해 전자를 플로팅 게이트에 주입, Vt를 원하는 값으로 조정한다. 3) **소거 모드**에서는 반대 전압을 가해 전자를 제거, Vt를 초기화한다. 이러한 모드 전환은 별도의 프로그래밍 로직(P)과 제어 신호(ERASE, PROG, FT_i, FC_j)로 구현된다.

가중치 프로그래밍을 위해 저자들은 기존 퍼셉트론 학습 알고리즘(PLA)을 회로 시뮬레이터와 결합한 **수정 퍼셉트론 학습 알고리즘**을 개발했다. 알고리즘은 목표 임계 함수 f =

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기