스핀트로닉 클러스터링을 위한 무감독 경쟁형 하드웨어 학습 규칙

초록

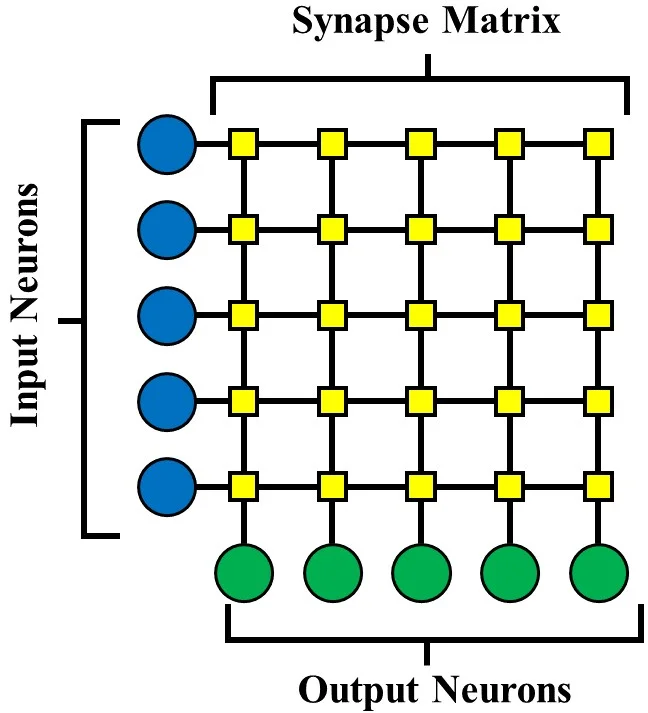

본 논문은 3단자 도메인월 DW‑MTJ 소자를 이용해 신경망 가중치를 전자적으로 업데이트하는 무감독 학습 회로를 제안한다. 교차배열 구조에서 4단자 뉴런이 피드백 전류를 생성해 3단자 시냅스의 도메인월 위치를 조정함으로써 Hebbian‑STDP 형태의 가중치 변화가 이루어지며, MNIST 및 의료·식물 데이터셋에서 클러스터링 정확도가 80% 이상에 도달한다.

상세 분석

이 연구는 스핀트로닉 디바이스의 물리적 특성을 신경망 학습 메커니즘에 직접 매핑한 점에서 혁신적이다. 먼저, 3단자 DW‑MTJ 시냅스는 전류에 의해 도메인월이 이동함으로써 MTJ의 저항(즉, 가중치)을 연속적으로 조정한다. 전류의 방향에 따라 반평행·평행 영역이 확대·축소되며, 이는 전통적인 아날로그 메모리의 프로그래밍과 유사하지만, 비휘발성·초저전력이라는 스핀트로닉 고유의 장점을 갖는다. 4단자 DW‑MTJ 뉴런은 LIF(Leaky‑Integrate‑and‑Fire) 동작을 수행하는데, 여기서 도메인월의 이동은 누적 전류에 비례하고, 누설 메커니즘은 도메인월을 역방향으로 이동시켜 자연스러운 시간적 소멸을 구현한다.

핵심적인 학습 회로는 뉴런의 출력 전류(I_FB)를 시냅스의 S2‑S1 단자에 피드백으로 연결한다. 뉴런이 스파이크를 발생하면 I_FB가 양(또는 음) 방향으로 흐르고, 이는 해당 시냅스의 도메인월을 이동시켜 가중치를 강화하거나 약화한다. 이 과정은 Hebbian 학습, 즉 “함께 활성화된 시냅스는 강화된다”는 원리를 전기적으로 구현한 것으로, STDP와 유사한 시냅스 가중치 변화를 제공한다. 또한, 뉴런의 이진 MTJ 저항(R_MTJ)은 피드백 전류의 크기를 조절해 학습률을 동적으로 제어한다—스파이크가 발생한 뉴런은 높은 전도 상태가 되어 강한 피드백을 제공하고, 비활성 뉴런은 낮은 전도 상태가 되어 학습을 억제한다.

수식적으로는 시냅스 가중치 ω_t가 도메인월 위치 x_t와 터널 장벽 폭 w에 의해 정의되고, 전류 I와 시간 ΔT에 비례하는 α 함수가 도메인월 이동량을 결정한다. 뉴런의 경우 누설 항 L이 포함된 동역학식이 도입돼, 경쟁적 억제(lateral inhibition)를 통해 매 입력마다 하나의 뉴런만 활성화되는 “winner‑take‑all” 동작을 보장한다. 이러한 구조는 전통적인 디지털 구현 대비 회로 복잡도와 에너지 소비를 크게 낮추면서도, 클러스터링과 같은 비지도 학습에 필요한 가중치 적응을 온칩에서 실현한다.

실험에서는 5×5 교차배열을 사용해 MNIST 손글씨와 Wisconsin 유방암, Iris 데이터셋에 대해 클러스터링을 수행하였다. 초기 무작위 가중치와 비교했을 때, 약 1,000개의 학습 샘플 이후 정확도가 급격히 상승해 80% 수준에 도달했으며, 이는 전통적인 k‑means나 SVM 대비 유사하거나 우수한 성능을 보인다. 또한, 학습 단계와 추론 단계가 명확히 분리되어 있어, 학습이 끝난 후에는 단순히 전류 흐름만으로 추론이 가능하다는 점도 강조된다.

이 논문의 한계는 현재 3‑단자 시냅스와 4‑단자 뉴런 간의 인터페이스가 아날로그 전류에 크게 의존한다는 점이다. 제조 공정 변동, 온도 변화 등에 따른 전류‑도메인월 변환 효율의 불확실성이 존재한다. 또한, 현재 구현은 5×5 규모에 국한돼 있어 대규모 네트워크 확장 시 라인 저항·전압 강하 문제와 전류 분배의 비선형성이 새로운 설계 과제로 남는다. 그럼에도 불구하고, 스핀트로닉 디바이스 자체가 비휘발성·저전력이라는 근본적인 장점을 제공하므로, 향후 CMOS‑스핀트로닉 하이브리드 시스템에서 온칩 학습을 구현하는 데 중요한 기반이 될 것으로 기대된다.

댓글 및 학술 토론

Loading comments...

의견 남기기