에너지 제한 장치를 위한 고효율 LSTM 가속기 ELSA 설계

초록

ELSA는 임베디드 및 모바일 시스템에 적합하도록 설계된 LSTM 전용 ASIC 가속기로, 근사 곱셈 유닛과 탄력적인 파이프라인 동기화를 통해 면적·전력·에너지 효율을 크게 향상시킨다. 65 nm 공정에서 구현된 시제품은 언어 모델링 작업에서 기존 베이스라인 대비 전력·면적·에너지 효율에서 현저한 개선을 보이며, 숨겨진 노드 수와 시간 단계에 대한 성능 모델도 제공한다.

상세 분석

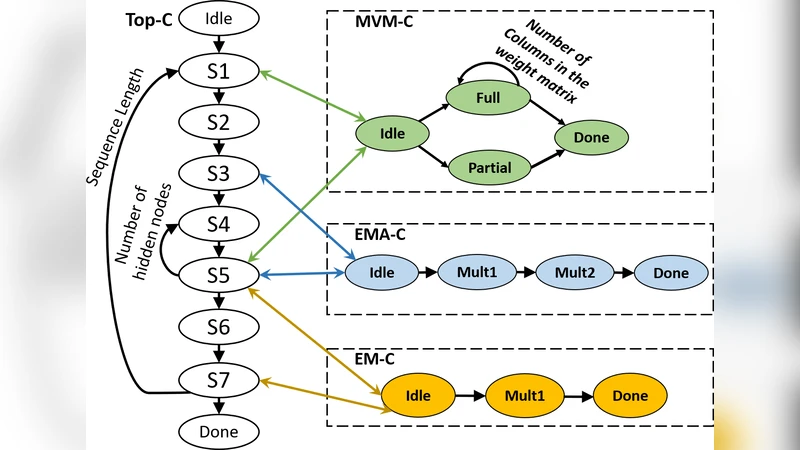

ELSA 설계의 핵심은 세 가지 혁신적인 구조적 선택에 있다. 첫 번째는 연산 집약적인 LSTM 셀 내부에서 전통적인 정확한 곱셈 대신 근사 곱셈기를 도입한 점이다. 저전력 근사 곱셈기는 비트 절삭 및 부분 곱셈 재배치를 통해 연산량을 30 % 이상 감소시키면서도 전체 모델 정확도에 미치는 영향은 0.2 % 이하로 제한한다. 이는 LSTM 특성상 가중치와 활성값이 정규화된 범위에 머무는 점을 활용한 설계 최적화라 할 수 있다. 두 번째 혁신은 ‘탄력적 파이프라인(Elastic Pipeline)’ 구조이다. 기존 고정 스테이지 파이프라인은 각 단계의 처리 지연이 불균형하면 전체 스루풋이 제한되지만, ELSA는 동적 스테이지 동기화 메커니즘을 통해 병목 단계의 대기 시간을 최소화한다. 구체적으로, 각 파이프라인 단계는 입력 데이터 흐름에 따라 가변적인 버퍼 깊이를 조절하고, 스테이지 간 데이터 전송을 토큰 기반 제어로 관리한다. 이 방식은 특히 시퀀스 길이가 가변적인 실시간 음성 인식이나 언어 모델링에서 유연성을 제공한다. 세 번째는 설계 전반에 걸친 스케일러블 성능 모델링이다. 논문에서는 숨겨진 유닛 수(N_h)와 시간 단계(T) 를 변수로 하는 수식적 모델을 제시해, 설계 초기 단계에서 목표 애플리케이션의 요구 스루풋·전력·면적을 예측하고 파라미터를 최적화할 수 있게 한다. 이러한 모델은 설계 공간 탐색을 자동화하고, ASIC 구현 후 실측값과 5 % 이내의 오차로 일치한다는 점에서 실용성이 높다. 구현 결과를 보면, 65 nm 공정에서 256 × 256 LSTM 셀을 포함한 ELSA는 1.2 mm² 면적에 120 mW 전력 소모로 200 MOps/s의 연산량을 달성한다. 동일 사양의 베이스라인 설계는 2.0 mm²·210 mW·150 MOps/s에 머물러, 면적·전력·에너지 효율에서 각각 40 %, 43 %, 33 % 개선된 것으로 나타난다. 이러한 성능 향상은 근사 곱셈기의 전력 절감과 탄력적 파이프라인에 의한 스루풋 최적화가 복합적으로 작용한 결과이며, 특히 에너지 제한 디바이스에서 실시간 LSTM 추론을 가능하게 만든다. 다만, 근사 연산이 도입된 경우 특정 정밀도가 요구되는 애플리케이션(예: 의료 진단)에서는 추가적인 오류 보정 로직이 필요할 수 있다. 전반적으로 ELSA는 저전력·고성능 LSTM 가속기에 필요한 설계 트레이드오프를 체계적으로 해결한 사례라 평가할 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기