RRAM 기반 이진 신경망의 비트 오류 내성 설명

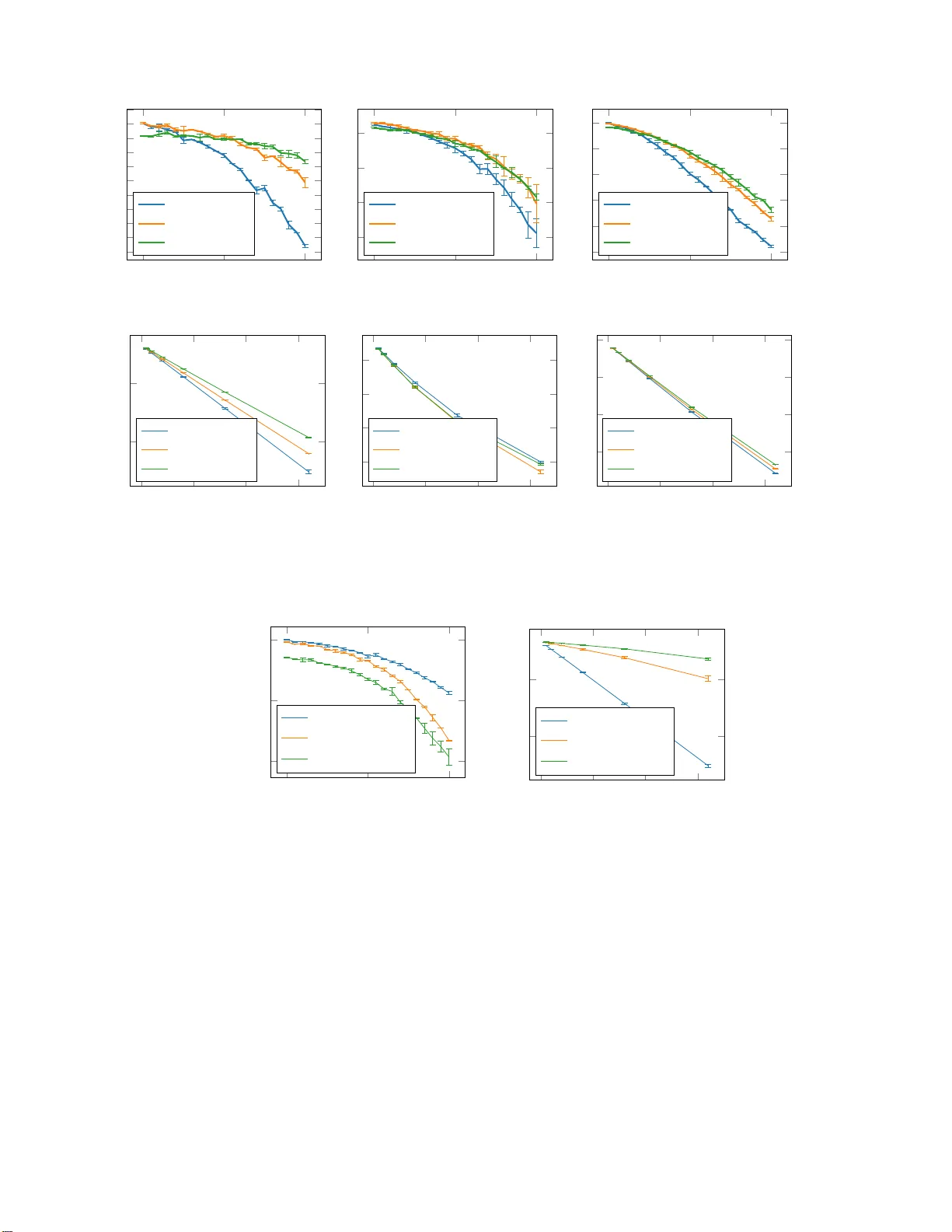

본 논문은 초저전력 RRAM의 높은 비트 오류율(≈3.3%)에도 불구하고 이진 신경망(BNN)이 견딜 수 있는 메커니즘을 탐구한다. 기존 방법이 오류율에 과적합되는 문제를 해결하기 위해 직통(STRAIGHT‑THROUGH) 그래디언트 근사를 적용한 가중치 부호 뒤집기 학습을 제안하고, 오류 내성을 직접 측정하지 않고도 예측할 수 있는 새로운 메트릭 T_b를 정의한다. 또한 T_b를 최적화하는 정규화 항을 도입해 정확도와 비트 오류 내성 사이의 …

저자: Sebastian Buschj"ager, Jian-Jia Chen, Kuan-Hsun Chen

**1. 서론 및 배경**

엣지 디바이스는 전력·연산·메모리 제약이 크기 때문에 경량화된 인공지능 모델이 필요하다. 이진 신경망(BNN)은 가중치를 ±1 로 이진화하고 XNOR·POPCOUNT 연산을 사용해 메모리와 연산량을 크게 절감한다. 그러나 BNN은 정확도가 전통적인 풀프리시전 모델보다 약간 낮으며, 메모리 구현에 따라 오류에 취약할 수 있다. 최근 비휘발성 메모리인 RRAM은 초저전력 설정에서 30배 낮은 프로그래밍 에너지를 제공하지만, 셀 프로그래밍 전압을 낮추면 비트 오류율이 3.3%까지 상승한다. Hirtzlin et al.은 훈련 시 무작위 비트 플립을 삽입해 BNN을 4%까지의 오류에 견디게 만들었지만, 오류 확률에 과적합(over‑fit)되는 문제와 훈련 복잡성 증가가 있었다.

**2. 목표**

본 논문은 (i) 기존 플립‑훈련의 과적합을 완화하고, (ii) 비트 오류 내성을 직접 측정하지 않고도 예측할 수 있는 메트릭을 정의하며, (iii) 메트릭을 활용해 정확도와 BET 사이의 트레이드오프를 조절하는 정규화 기법을 제시한다.

**3. BNN 기본 구조와 STE**

BNN은 실수 가중치를

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기