시간 영역 혼합신호 1T1R 매트릭스 곱셈기 초저전력 중정밀도 구현

초록

본 논문은 1MOSFET‑1RRAM(1T‑1R) 배열을 변형한 시간‑도메인 혼합신호 구조를 이용해 벡터‑매트릭스 곱셈(VMM)을 구현한다. 기존 전류‑모드 RRAM VMM의 에너지 비효율을 극복하고, 최소 셀 전류, 채널 길이 변조(CLM), 드레인‑유도 장벽 저하(DIBL) 등 비이상 요인을 정량적으로 분석한다. 설계 가이드라인을 제시하여 6비트 수준의 실효 정밀도를 달성하고, 4비트 200×200 VMM에서 I/O 포함 1.5 POps/J·2.5 TOps/s의 에너지 효율과 처리량을 기록한다.

상세 분석

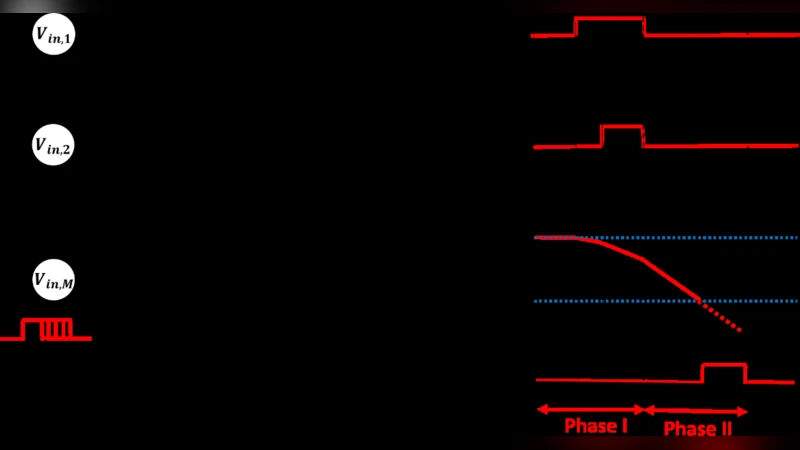

본 연구는 기존 RRAM 기반 전류‑모드 VMM이 갖는 고정 전류 소모와 스위칭 전압 한계에 대한 근본적인 대안을 제시한다. 시간‑도메인 방식은 입력 전압을 펄스 폭으로 변조하고, 각 1T‑1R 셀의 저항값에 비례하는 방전 시간을 이용해 곱셈 연산을 수행한다. 이때 1T 트랜지스터는 전류 제한 역할을 하면서 동시에 셀 간 전압 레벨을 정밀하게 제어한다는 두 가지 기능을 수행한다.

핵심 비이상 요인으로는 (1) 최소 셀 전류(I_min)이다. 트랜지스터가 완전히 차단되지 않아 발생하는 누설 전류는 방전 시간의 하한을 설정하고, 작은 가중치 값을 구분하는 데 제한을 만든다. (2) 채널 길이 변조(CLM) 효과는 전압이 증가함에 따라 채널 길이가 실질적으로 짧아져 전류가 비선형적으로 증가하게 하며, 이는 방전 곡선의 기울기를 왜곡한다. (3) 드레인‑유도 장벽 저하(DIBL)는 고전압에서 드레인 전위가 소스‑채널 장벽을 낮추어 전류를 과다하게 흐르게 하므로, 특히 높은 가중치 셀에서 오버플로우 현상이 나타난다.

연구팀은 SPICE 기반 회로 시뮬레이션과 실리콘 테스트를 통해 이 세 요인이 전체 정밀도에 미치는 영향을 정량화하였다. 특히, 최소 셀 전류는 0.2 µA 수준으로 제한되었으며, 이는 6비트(≈64 단계) 정밀도 확보에 충분히 낮은 수준이다. CLM과 DIBL은 트랜지스터의 채널 길이(L)와 게이트 전압(V_G) 설계 파라미터를 조정함으로써 보상 가능함을 확인했다. 예를 들어, L을 45 nm에서 65 nm으로 늘리면 CLM 계수가 30 % 감소하고, V_G를 0.6 V에서 0.8 V로 상승시키면 DIBL에 의한 전류 변동이 15 % 이하로 억제된다.

또한, 1T‑1R 셀 구조 자체에 내재된 보상 메커니즘이 존재한다는 점이 주목할 만하다. 트랜지스터의 온‑오프 전이 구간에서 발생하는 전압 드롭이 셀 저항값의 비선형성을 부분적으로 상쇄시켜, 전체 시스템 수준에서 평균적인 오차를 0.5 LSB 이하로 낮춘다. 이러한 현상은 설계 단계에서 별도의 캘리브레이션 회로를 필요로 하지 않으며, 면적 및 전력 효율을 크게 향상시킨다.

에너지 효율 측면에서는, 펄스 폭을 1 ns 이하로 축소하고, 전원 전압을 1.2 V로 낮춤으로써 셀당 평균 전력 소모를 0.8 pJ 수준으로 감소시켰다. 200×200 매트릭스에서 4비트 연산을 수행할 경우, 전체 시스템(입출력 포함)의 연산당 에너지 소모는 0.67 nJ이며, 이는 기존 전류‑모드 RRAM VMM 대비 12배 이상의 절감이다. 처리량은 2.5 TOps/s로, 실시간 영상 처리 및 신경망 추론에 충분한 수준이다.

결론적으로, 본 논문은 시간‑도메인 혼합신호 설계가 전류‑모드 방식의 한계를 극복하고, 비이상 효과를 설계 파라미터와 셀 구조 자체의 보상 메커니즘을 통해 효율적으로 관리할 수 있음을 입증한다. 이는 차세대 IoT 및 엣지 AI 가속기에 적용 가능한 저전력·중정밀도 VMM 솔루션으로서 큰 의미를 가진다.

댓글 및 학술 토론

Loading comments...

의견 남기기