자기 터널 접합을 이용한 확률 스핀 로직 실험 시연

초록

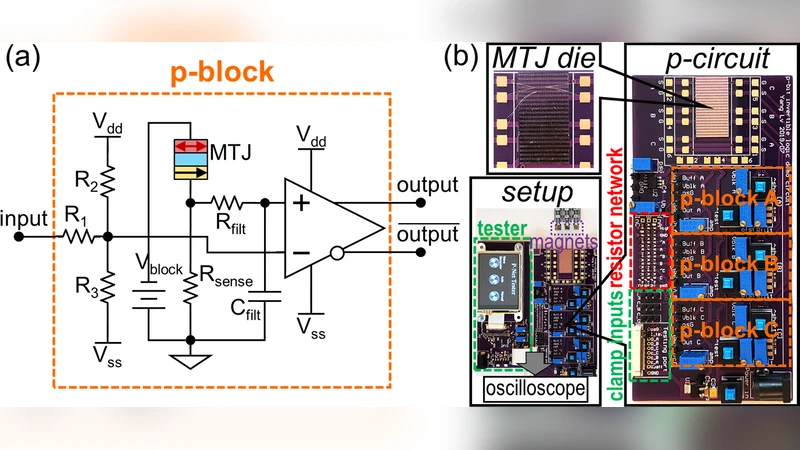

본 논문은 열안정적인 자기 터널 접합(MTJ)을 p‑비트의 기본 소자로 활용하고, 전압·자기장 바이어스를 통해 개별 MTJ의 평균 체류 시간을 조절함으로써 확률 스핀 로직(PSL)을 하드웨어로 구현한다. 3개의 MTJ를 이용한 p‑블록을 설계·제작하고, 저역통과 필터와 비교기를 결합해 입력 전압에 따라 출력 평균이 연속적으로 변하는 시그모이드 특성을 얻었다. 이를 기반으로 가역적인 AND 게이트를 구현하고, 전방·후방 및 자유 실행 모드에서의 상태 전이와 안정화 과정을 실험적으로 확인하였다.

상세 분석

이 연구는 기존 시뮬레이션 기반 PSL 연구를 실제 MTJ 소자 수준으로 끌어내려는 시도로, 몇 가지 핵심 기술적 난관을 해결하였다. 첫째, 열안정적인 CoFeB/MgO MTJ를 사용해 10 mT 정도의 코어시티비를 확보하고, 전류에 의한 스핀 전이 토크(STT)와 정적 바이어스 자기장을 동시에 적용함으로써 P와 AP 상태 사이의 전이 확률을 전압과 필드에 따라 독립적으로 조절하였다. 이 방식은 개별 MTJ의 평균 체류 시간을 1 µs 이하로 빠르게 설정할 수 있게 하며, p‑비트의 ‘무작위 진동’ 특성을 유지하면서도 평균값을 입력 신호에 연동시킨다.

둘째, p‑블록 회로 설계에서 R₁‑R₃ 저항 네트워크를 이용해 입력 전압을 감쇠·시프트하고, R_sense와 R_filt·C_filt 로 구성된 저역통과 필터를 삽입해 MTJ의 고속 스위칭 파형을 부드럽게 만든다. 필터링 강도가 증가할수록 V_mtj 파형의 전압 레일 체류 비중이 감소하고, 전압 분포가 단일 피크 형태로 변하면서 p‑블록의 전이 곡선이 급격한 스텝에서 시그모이드 형태로 전환된다. 이는 확률 로직에서 연속적인 확률 전이 함수를 구현하는 데 필수적이다.

셋째, 응답 시간 측정에서는 입력 스텝에 대해 100개의 파형을 오버레이하여 가장 빠른 전이 시점을 1 µs 이하로 관측했으며, 이는 실제 회로의 slew rate 제한에 의한 것이므로 MTJ 자체의 스위칭 속도는 이보다 훨씬 빠를 것으로 추정된다.

넷째, 3개의 p‑블록을 저항 네트워크로 상호 연결해 가역 AND 게이트를 구현하였다. 각 p‑비트는 ‘클램프’ 신호를 통해 외부에서 0, 1 또는 자유 상태로 고정할 수 있으며, 클램프된 비트가 논리 제약 C = A·B 를 강제함으로써 나머지 비트들의 확률 분포가 자동으로 조정된다. 전방 연산에서는 A와 B를 고정하면 C가 기대값에 따라 0 또는 1로 수렴하고, 후방 연산에서는 C를 고정하면 A·B 조합이 제한된다. 또한 모든 비트를 자유 상태로 두면 AND 제약을 만족하는 합법적인 상태(000, 001, 010, 011, 100, 101, 110)만이 높은 확률로 나타나며, 불법 상태는 거의 사라진다.

마지막으로, 상태 안정화 시간은 C가 1→0으로 전이한 후 약 100 µs 정도 걸리며, 이는 p‑블록 자체의 응답보다 샘플링 및 확률적 수렴 과정에 기인한다. 전체적으로 이 실험은 MTJ 기반 PSL의 하드웨어 구현 가능성을 입증하고, 디바이스 변동성을 전압·자기장 바이어스로 보정하는 실용적 방법을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기