저해상도 RRAM으로 구현한 초고해상도 신경망 기반 ADC 설계

본 논문은 3‑bit 수준의 저정밀 RRAM 소자를 활용해 14‑bit 초고해상도 아날로그‑디지털 변환기를 구현하는 방법을 제시한다. 파이프라인형 하드웨어 구조와 맞춤형 신경망 학습 프레임워크를 공동 설계(co‑design)함으로써, 각 단계가 1∼3‑bit만을 담당하도록 하고 이를 연쇄적으로 결합해 전체 해상도를 크게 높인다. SPICE 시뮬레이션 결과, 전력·속도 면에서 기존 NN‑ADC 대비 우수한 FoM을 달성했으며, 선형 및 비선형 양…

저자: Weidong Cao, Liu Ke, Ayan Chakrabarti

본 논문은 저정밀(3‑bit) RRAM 소자를 이용해 14‑bit 초고해상도 아날로그‑디지털 변환기(ADC)를 구현하는 새로운 설계 방법론을 제시한다. 기존 NN‑ADC 연구들은 RRAM 셀을 6∼12‑bit 수준으로 가정하고 4∼8‑bit ADC를 설계했지만, 실제 대량 생산 공정에서는 2∼4‑bit 정도의 정밀도가 일반적이다. 이러한 현실적인 제약을 극복하기 위해 저자는 파이프라인형 하드웨어 구조와 맞춤형 신경망 학습 프레임워크를 공동 설계(co‑design)한다.

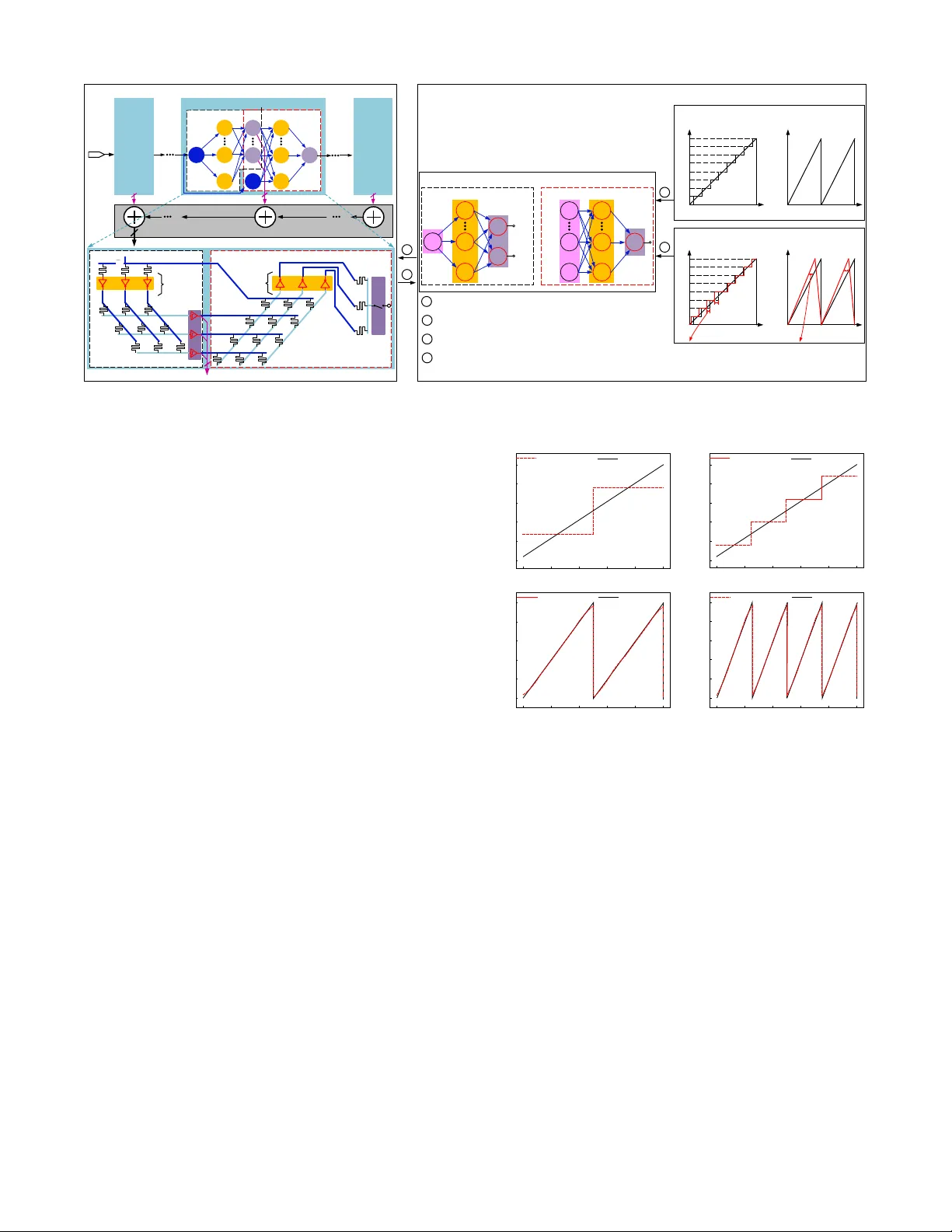

파이프라인 ADC는 여러 단계가 순차적으로 작동해 각 단계가 낮은 비트 수(N_i=1∼3)를 담당하고, 잔차(residue)를 증폭해 다음 단계에 전달한다. 이렇게 하면 전체 해상도는 각 단계의 비트 수 합으로 누적되지만, 개별 단계는 저정밀도 RRAM으로도 충분히 구현 가능하다. 논문에서는 각 단계에 5‑layer MLP(다층 퍼셉트론)를 배치하고, 이를 두 개의 3‑layer 서브‑네트워크(서브‑ADC와 잔차 블록)로 분할한다. 서브‑ADC는 입력 아날로그 신호를 하나의 “플레이스홀더” 뉴런으로 받아들여, 은닉층(H_F,i)과 출력층(S_i) 사이의 가중치를 학습한다. 여기서 Smooth 코드(예: 3→2 부드러운 코드)를 사용해 전통적인 이진 인코딩을 대체함으로써 학습 정확도를 높이고 은닉층 규모를 줄인다. 잔차 블록은 (1+S_i)개의 입력(아날로그 잔차와 서브‑ADC 디지털 코드)과 하나의 아날로그 출력을 갖으며, 은닉층(H_R,i)과 출력층 사이의 가중치를 통해 잔차 함수를 근사한다. 전통적인 연산 증폭기(op‑amp)를 제거하고 CMOS 인버터 기반 전압 전송 특성(VTC)을 활용해 전력 소모를 크게 절감한다.

학습 프레임워크는 하드웨어 제약을 비용 함수에 반영한다. 구체적으로, RRAM의 3‑bit 양자화 노이즈를 모델링하고, 전체 파이프라인 출력이 목표 디지털 코드와 얼마나 차이나는지를 최소화한다. 각 단계는 독립적으로 역전파(back‑propagation) 과정을 거쳐 최적화되며, 단계별 잔차 전파를 고려해 전체 시스템이 조화롭게 동작하도록 설계한다. 설계 공간 탐색에서는 N_i=1,2,3 조합을 모두 시험해 전력·면적·속도 트레이드오프를 정량화했다. 최적 구성은 14‑bit 전체 해상도를 달성하기 위해 1‑bit, 2‑bit, 3‑bit 스테이지를 적절히 배치한 구조이며, 각 스테이지는 3‑bit RRAM으로 구현된다.

시뮬레이션은 45 nm CMOS와 3‑bit RRAM 모델을 기반으로 SPICE 환경에서 수행되었다. 주요 결과는 다음과 같다. (1) 14‑bit 정밀도 달성, 평균 SNR > 70 dB; (2) 전력 소모는 기존 6‑bit RRAM 기반 NN‑ADC 대비 약 30 % 감소; (3) 샘플링 레이트는 200 MS/s 이상, 변환 지연 5 ns 이하로 고속 애플리케이션에 적합; (4) 비선형 양자화(예: 로그 스케일)도 동일 구조에서 재학습만으로 구현 가능하며, 변환 속도와 에너지 효율이 유지된다.

이 연구는 세 가지 주요 기여를 가진다. 첫째, RRAM 공정 한계를 현실적으로 반영한 설계 흐름을 제시해 신경망 기반 하드웨어 가속기의 실용성을 높인다. 둘째, 파이프라인 구조와 신경망 근사를 결합한 새로운 설계 패러다임을 제시해 기존 아날로그 설계와 디지털 학습 기법 사이의 경계를 허문다. 셋째, 부드러운 코드와 잔차 기반 학습을 통해 비선형 양자화까지 손쉽게 확장 가능하므로, 근거리 센서 네트워크, 바이오 신호 처리 등 맞춤형 양자화가 요구되는 분야에 바로 적용할 수 있다.

향후 연구 과제로는 실제 실리콘‑RRAM 프로토타입 제작을 통한 공정 변동성, 온도·전압 드리프트 등에 대한 견고성 검증이 있다. 또한 다중 채널 파이프라인, 온‑칩 온라인 학습 기능을 추가해 실시간 적응형 양자화 시스템을 구현하는 것이 기대된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기