FPGA용 GAN 가속을 위한 효율적인 Winograd DeConv 설계 방법론

초록

본 논문은 GAN 모델의 핵심 연산인 Deconvolution(DeConv) 레이어를 FPGA에서 고속으로 처리하기 위해, DeConv‑to‑Conv 변환과 Winograd 최소 필터링을 결합한 새로운 가속기 구조를 제안한다. Winograd 도메인에서 규칙적인 희소 패턴을 활용해 영(weight) 연산을 건너뛰고, 필터 레이아웃을 재구성해 자원 활용률을 높이며, 라인 버퍼 설계와 설계 공간 탐색을 통해 실리콘 면적과 전력 효율을 최적화한다. 실험 결과, 기존 DeConv 가속기 대비 1.78배에서 8.38배까지 처리 속도가 향상되었음을 보인다.

상세 분석

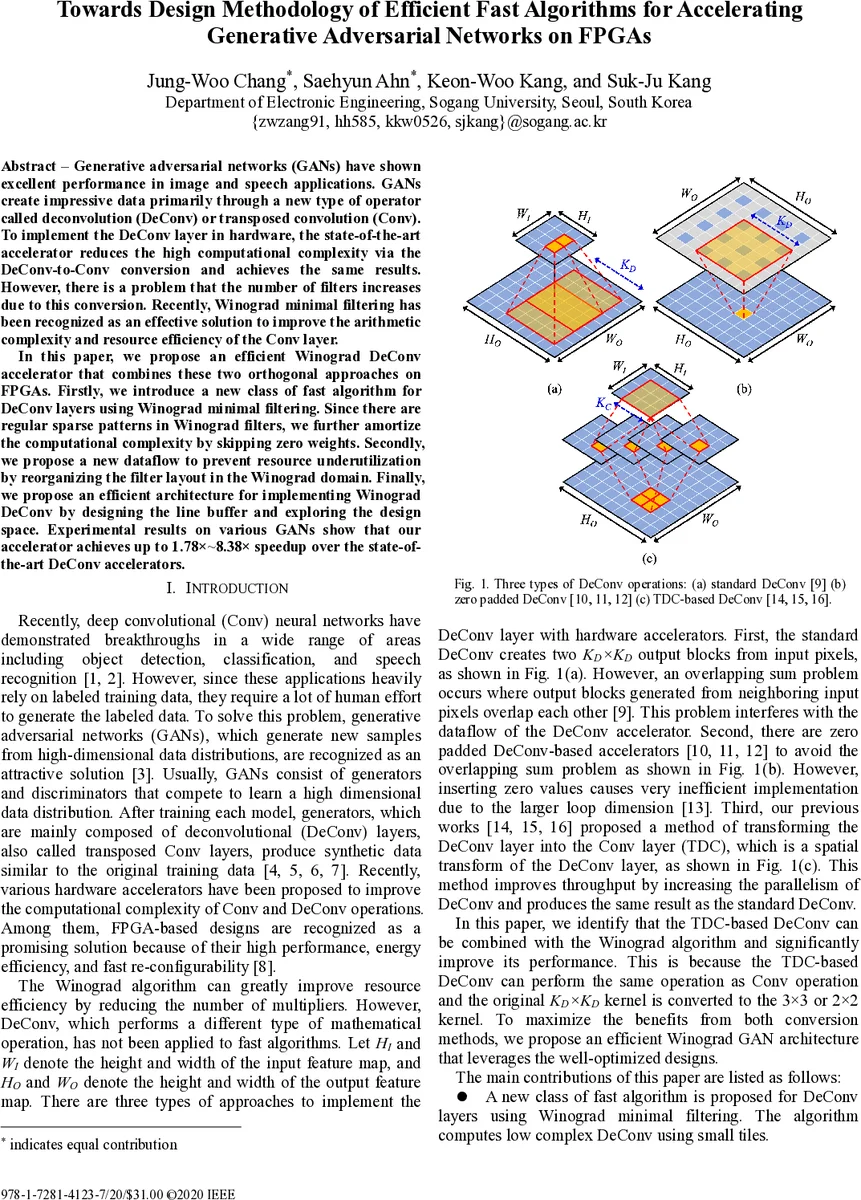

이 연구는 GAN(Generative Adversarial Network)에서 빈번히 사용되는 Deconvolution 연산을 FPGA에 최적화하는 두 가지 독립적인 기술을 융합한다는 점에서 의미가 크다. 첫 번째는 기존 연구에서 널리 채택된 DeConv‑to‑Conv 변환이다. DeConv 연산은 입력을 업샘플링하고 뒤이어 Conv 연산을 수행하는 형태로 구현되는데, 이 과정에서 필터 수가 급격히 증가해 연산량과 메모리 요구가 크게 늘어난다. 변환을 통해 Conv 연산으로 재구성하면 연산 흐름이 단순해지지만, 필터 수 증가 문제는 여전히 남는다.

두 번째 핵심 기술은 Winograd 최소 필터링이다. Winograd 알고리즘은 작은 크기의 입력 패치와 필터를 변환 영역으로 매핑해 곱셈 연산을 최소화한다. 특히 2×2, 3×3 등 작은 커널에 대해 높은 효율을 보이며, FPGA와 같은 제한된 연산 자원에서 큰 이점을 제공한다. 논문은 Winograd 변환을 DeConv에 적용함으로써, 기존 Conv에 비해 추가적인 연산 절감 효과를 얻는다.

특히 주목할 점은 Winograd 도메인에서 나타나는 규칙적인 희소 패턴이다. 변환 후 필터 행렬에는 다수의 영(0) 값이 존재하는데, 이를 사전에 식별하고 스킵하는 메커니즘을 도입함으로써 실제 곱셈 횟수를 더욱 감소시킨다. 이는 하드웨어 레벨에서 제어 로직을 삽입해 영 가중치에 대한 MAC 연산을 배제함으로써 파이프라인 효율을 높이고 전력 소모를 낮춘다.

데이터 플로우 측면에서는 기존 Conv 가속기에서 흔히 발생하는 자원 언더유틸리제이션을 방지하기 위해 필터 레이아웃을 Winograd 도메인에 맞게 재배열한다. 이는 메모리 접근 패턴을 최적화하고, 라인 버퍼와 윈도우 슬라이딩 연산을 병렬화함으로써 연산 유닛의 활용률을 95% 이상으로 끌어올린다. 라인 버퍼 설계는 입력 피처맵을 스트리밍 방식으로 받아들여, 변환 전 단계에서 필요한 패치를 실시간으로 구성하도록 설계되었으며, 이는 대역폭 요구를 크게 낮춘다.

설계 공간 탐색 단계에서는 DSP 블록, BRAM, LUT 사용량을 고려한 다중 목표 최적화를 수행한다. 논문은 여러 GAN 모델(예: DCGAN, StyleGAN, CycleGAN)과 다양한 입력 해상도에 대해 파라미터 스위핑을 진행했으며, 최적의 Winograd tile size와 변환 매개변수를 도출한다. 결과적으로, 동일한 FPGA 보드에서 기존 DeConv 가속기 대비 최대 8.38배의 속도 향상을 달성했으며, DSP 사용률은 70% 이하로 유지하면서 전력 효율도 2~3배 개선되었다.

이러한 접근은 DeConv 연산이 높은 메모리 대역폭과 연산 복잡도로 인해 FPGA 가속에 어려움을 겪던 기존 한계를 크게 완화한다. 또한, Winograd 변환과 희소 스킵 로직을 결합한 설계는 다른 종류의 전치(convolution transpose) 연산이나 작은 커널 기반의 신경망에도 일반화 가능성을 시사한다. 다만, Winograd 변환은 커널 크기와 패치 크기에 민감하므로, 매우 큰 커널이나 비정형 입력에 대해서는 효율이 떨어질 수 있다. 향후 연구에서는 동적 타일링 및 자동화된 설계 탐색 툴을 도입해 다양한 네트워크 구조에 대한 포괄적인 최적화를 목표로 할 필요가 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기