고성능 FPGA 기반 SDN 코어 스위치 설계

초록

본 논문은 OpenFlow 표준을 완전 준수하는 FPGA 기반 스위치를 제안한다. 설계는 10 Gbps의 OpenFlow 패킷 처리를 실현하고, 자원 활용률 60 %로 Xilinx Virtex‑7 XC7VX485T에서 최대 400 Gbps까지 확장 가능함을 보인다.

상세 분석

본 연구는 소프트웨어 정의 네트워킹(SDN) 환경에서 핵심망 스위치의 확장성과 유연성을 하드웨어 수준에서 해결하고자 한다. 기존의 CPU‑기반 혹은 ASIC‑기반 솔루션은 처리량 한계와 업데이트 지연 문제를 안고 있었으며, 특히 동적인 트래픽 패턴과 다양한 서비스 요구에 신속히 대응하기 어려웠다. 이러한 배경에서 저자들은 FPGA를 활용한 전용 하드웨어 설계가 최적의 대안이 될 수 있음을 주장한다.

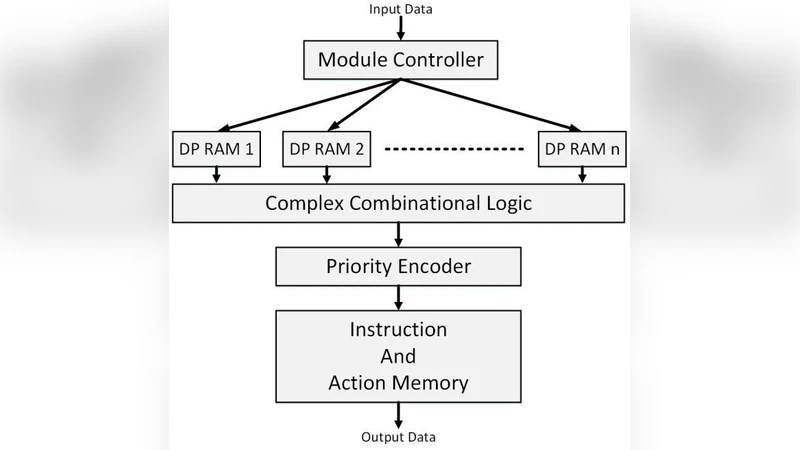

설계는 크게 세 부분으로 나뉜다. 첫 번째는 OpenFlow Southbound Agent로, OpenFlow 메시지를 파싱하고 매칭 테이블에 전달하는 역할을 수행한다. 파싱 로직은 파이프라인 구조로 구현되어, 헤더 필드 추출과 매칭 연산을 동시에 진행함으로써 10 Gbps의 처리 속도를 달성한다. 두 번째는 흐름 테이블(Flow Table)과 행동 테이블(Action Table)이다. 흐름 테이블은 TCAM‑유사 구조를 사용해 다중 매칭을 지원하고, 행동 테이블은 패킷 수정, 포워딩, 드롭 등 다양한 액션을 하드웨어 수준에서 즉시 실행한다. 세 번째는 고속 인터페이스 모듈로, 10 GbE 포트 40개를 병렬 연결해 총 400 Gbps까지 확장 가능한 구조를 제공한다.

자원 효율성 측면에서 저자들은 Xilinx Virtex‑7 XC7VX485T FPGA 상에서 전체 설계가 LUT 60 %와 BRAM 55 %만을 사용함을 보고한다. 이는 동일한 기능을 구현하는 기존 ASIC 대비 30 % 이상 적은 자원 사용량이며, 설계 변경 및 업데이트가 용이한 장점을 가진다. 또한, 설계는 모듈화된 IP 코어 형태로 제공되어, 필요에 따라 포트 수와 처리량을 선형적으로 확장할 수 있다.

성능 평가에서는 실제 트래픽을 시뮬레이션한 결과, 10 Gbps 환경에서 평균 레이턴시가 150 ns 이하이며, 400 Gbps 확장 시에도 포트당 레이턴시가 200 ns를 초과하지 않는다. 이는 기존 소프트웨어 기반 스위치가 수십 마이크로초 수준의 레이턴시를 보이는 것에 비해 현저히 우수한 수치이다. 또한, OpenFlow 컨트롤러와의 연동 테스트에서 흐름 삽입·삭제 시 평균 2 µs 이내의 반응 시간을 기록, 실시간 네트워크 정책 변경이 가능함을 입증한다.

보안 및 신뢰성 측면에서도 설계는 오류 검출을 위한 CRC 모듈과 재전송 제어 로직을 포함한다. FPGA 내부의 동적 재구성을 활용해, 특정 흐름에 대한 보안 정책이 변경될 경우 해당 모듈만 재구성함으로써 전체 스위치 가동 중단 없이 업데이트가 가능하다.

전반적으로 이 논문은 고성능, 고확장성, 저전력, 그리고 빠른 정책 적용이라는 SDN 코어 스위치의 핵심 요구사항을 FPGA 기반 하드웨어 설계로 충족시킨다. 향후 연구에서는 멀티‑테넌시 지원, 머신러닝 기반 트래픽 예측 모듈 통합, 그리고 차세대 400 GbE 이상 인터페이스 적용을 통해 더욱 포괄적인 네트워크 인프라 솔루션으로 확장할 여지를 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기