다중 정밀도 다중 연산 CNN 가속기 자동 생성 프레임워크 토마토

Tomato는 CNN 모델을 레이어별로 서로 다른 정밀도와 연산 방식을 적용해 자동으로 FPGA 가속기를 생성하는 프레임워크이다. 하이브리드 양자화를 통해 시프트(2의 거듭제곱)와 고정소수점 연산을 혼합하고, 탐색 알고리즘으로 정확도와 하드웨어 비용을 동시에 만족하는 구성을 찾는다. 생성된 가속기는 플랫 스트리밍 파이프라인 구조를 사용해 각 레이어에 전용 연산 코어와 버퍼를 배치하고, 필요에 따라 언롤링 비율을 조정해 처리량을 맞춘다. Mobi…

저자: Yiren Zhao, Xitong Gao, Xuan Guo

본 논문은 FPGA 상에서 고성능 딥러닝 추론을 구현하기 위한 자동화 설계 프레임워크인 Tomato를 제안한다. 기존 FPGA 기반 CNN 가속기들은 대부분 하나의 연산 유형과 고정된 정밀도를 전체 레이어에 적용하는 homogeneous systolic array 방식을 채택해 왔다. 이러한 설계는 다양한 커널 크기·채널 수·스트라이드 등을 가진 현대 CNN에 비효율적이며, 특히 대규모 모델을 온‑칩 메모리만으로 구현하기 어렵다. Tomato는 이러한 한계를 극복하기 위해 두 가지 핵심 아이디어를 도입한다.

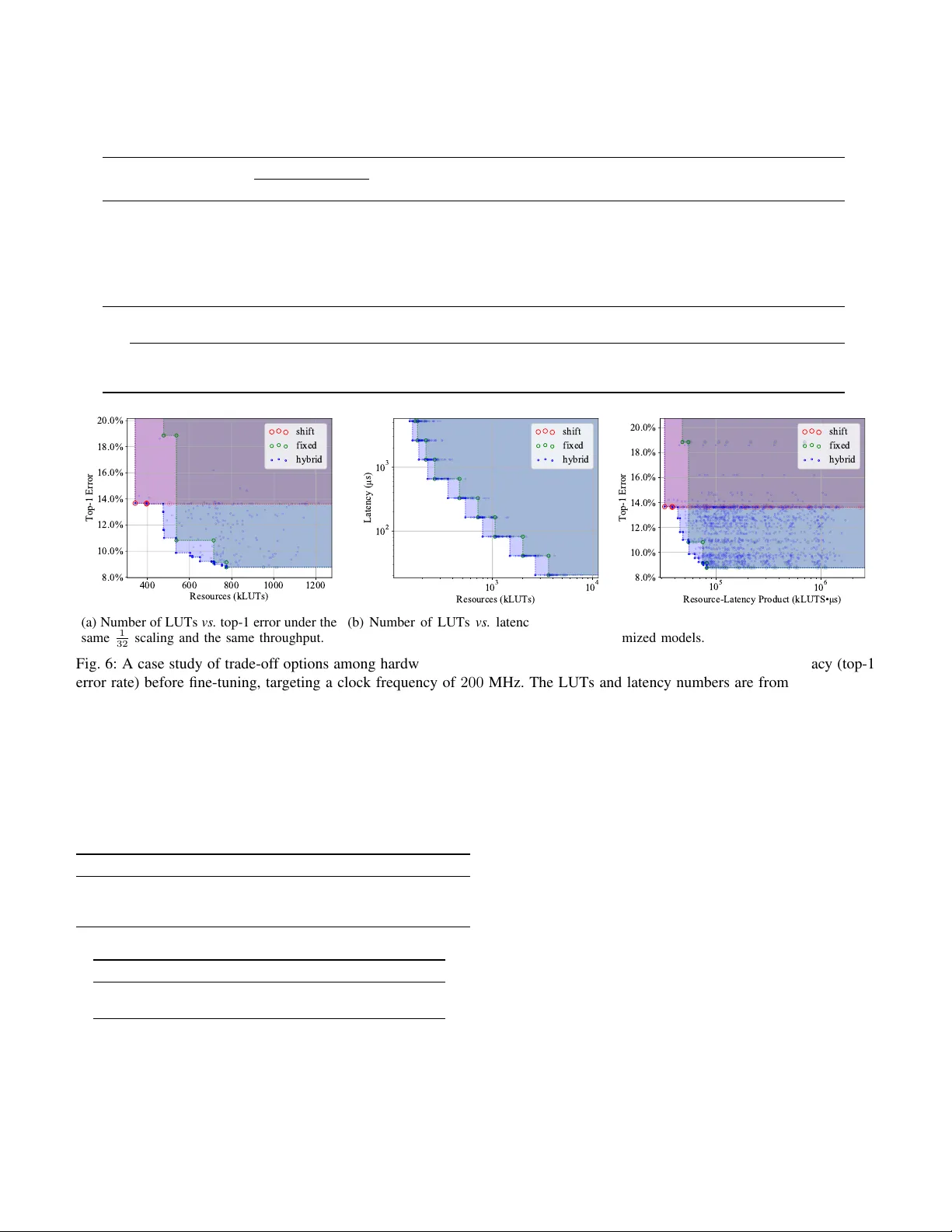

첫 번째는 ‘하이브리드 양자화(Hybrid Quantization)’이다. 레이어별로 시프트 양자화(2의 거듭제곱 가중치)와 고정소수점 양자화를 혼합하여 사용한다. 시프트 양자화는 배럴 쉬프터만으로 곱셈을 대체해 논리 사용량과 전력 소모를 크게 줄이며, 고정소수점 양자화는 정밀도가 높은 연산이 필요한 레이어에 적용한다. 양자화 방식을 선택하는 과정은 탐색 알고리즘(Algorithm 1)으로 자동화된다. 이 알고리즘은 초기 8‑bit 고정소수점 모델에서 시작해 레이어당 비트폭을 1비트씩 감소시키거나 연산 방식을 전환하면서 하드웨어 비용 감소량을 최대화한다. 탐색은 지정된 정확도 하한(원본 정확도의 95 %)과 하드웨어 자원 제한을 동시에 만족할 때까지 진행된다. 탐색 후에는 짧은 재학습(fine‑tune) 단계가 포함돼 양자화로 인한 정확도 손실을 회복한다.

두 번째는 ‘플랫 스트리밍(Flattened Streaming) 아키텍처’이다. 각 컨볼루션 레이어마다 전용 연산 코어, 슬라이드 버퍼, 가중치 버퍼를 배치하고, 이들 코어를 스트림 형태로 연결해 완전 파이프라인을 구성한다. 레이어 간에 중간 결과를 온‑칩 버퍼에만 저장하고, 외부 DRAM 접근을 배제함으로써 메모리 대역폭 병목을 제거한다. 또한 레이어별 연산 방식이 독립적이므로 시프트 연산을 사용하는 레이어는 배럴 쉬프터만, 고정소수점 연산을 사용하는 레이어는 짧은 고정소수점 멀티플라이어를 사용한다. 이를 통해 DSP 사용을 최소화하고, LUT와 BRAM 사용을 최적화한다.

Tomato는 하드웨어 비용 추정기를 통해 각 레이어의 연산량과 데이터 흐름을 분석하고, ‘throughput matching’ 블록을 자동 삽입한다. 이 블록은 앞선 레이어가 생성하는 출력 속도와 뒤따르는 레이어가 요구하는 입력 속도를 일치시키기 위해 언롤링 팩터와 파이프라인 깊이를 조정한다. 결과적으로 레이어 간 스톨을 방지하고, 전체 파이프라인의 이용률을 80 % 이상 유지한다.

실험에서는 MobileNet‑V1을 대상으로 단일 Xilinx UltraScale+ FPGA에 전체 ImageNet 모델을 구현하였다. 하이브리드 양자화 후 모델 파라미터는 약 30 % 감소했으며, 연산 복잡도는 2‑3배 감소하였다. 최종 가속기는 오프‑칩 메모리 없이 3000 FPS 이상의 처리량을 달성했고, 기존 최첨단 FPGA 기반 가속기 대비 지연 시간과 처리량에서 2‑4배 향상을 보였다. 또한 다중 FPGA 구성에서도 동일한 자동화 흐름으로 스케일링이 가능함을 시연하였다.

본 논문의 주요 기여는 다음과 같다. (1) 레이어별 정밀도·연산을 최적화하는 하이브리드 양자화 기법과 그 자동 탐색 알고리즘을 제시하였다. (2) 플랫 스트리밍 파이프라인을 기반으로 한 새로운 아키텍처를 설계해 온‑칩 자원만으로 대규모 CNN을 구현하였다. (3) 전체 소프트웨어‑하드웨어 공동 설계 흐름을 자동화해, 사용자가 CNN 모델만 제공하면 FPGA 가속기를 자동으로 생성할 수 있는 프레임워크를 구현하였다. (4) 실험을 통해 제안된 방법이 기존 FPGA 기반 가속기 대비 지연·처리량·자원 효율성에서 현저히 우수함을 입증하였다.

이러한 결과는 FPGA가 엣지 및 클라우드 환경에서 딥러닝 추론을 수행할 때, 높은 처리량과 낮은 지연을 동시에 만족시키는 실용적인 솔루션을 제공한다는 점에서 큰 의미를 가진다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기