단일 MOSFET 고해상도·고신뢰 머신러닝 분류기

본 논문은 입력 피처와 가중치를 각각 MOSFET의 바디와 게이트에 연결해 단일 트랜지스터로 고해상도 곱셈‑누적(MAC)을 구현한다. 서브스레시홀드 동작과 트리플‑웰 공정을 이용해 전력 6.2 pJ·결정⁻¹, 면적 2,179 µm²를 달성했으며, 9×9 다운샘플링된 MNIST 데이터셋에서 90 % 정확도와 PVT 변동에 대한 안정성을 보였다. 또한 OVA 방식과 전압 차 기반 신뢰도 추출을 결합한 “CORE” 구조를 제안한다.

저자: Farid Kenarangi, Inna Partin-Vaisb

본 논문은 전력·면적 효율이 중요한 엣지 컴퓨팅 환경을 위해, 아날로그‑디지털 혼합 설계 기반의 고신뢰·고해상도 머신러닝 분류기(CORE)를 제안한다. 기존 디지털 분류기는 피처와 가중치를 디지털화하고 고비트 연산을 수행함으로써 전력 소모와 면적이 크게 증가한다. 반면, 제안된 구조는 피처와 가중치를 각각 MOSFET의 바디와 게이트에 직접 연결해 단일 트랜지스터가 곱셈 연산을 수행하도록 설계하였다. 이때 바디 전압은 피처 값에 비례하도록, 게이트 전압은 가중치 절댓값에 매핑한다. 양·음 가중치를 구분하기 위해 별도의 라인을 사용하고, 각 MOSFET은 양성 또는 음성 라인에 연결된다.

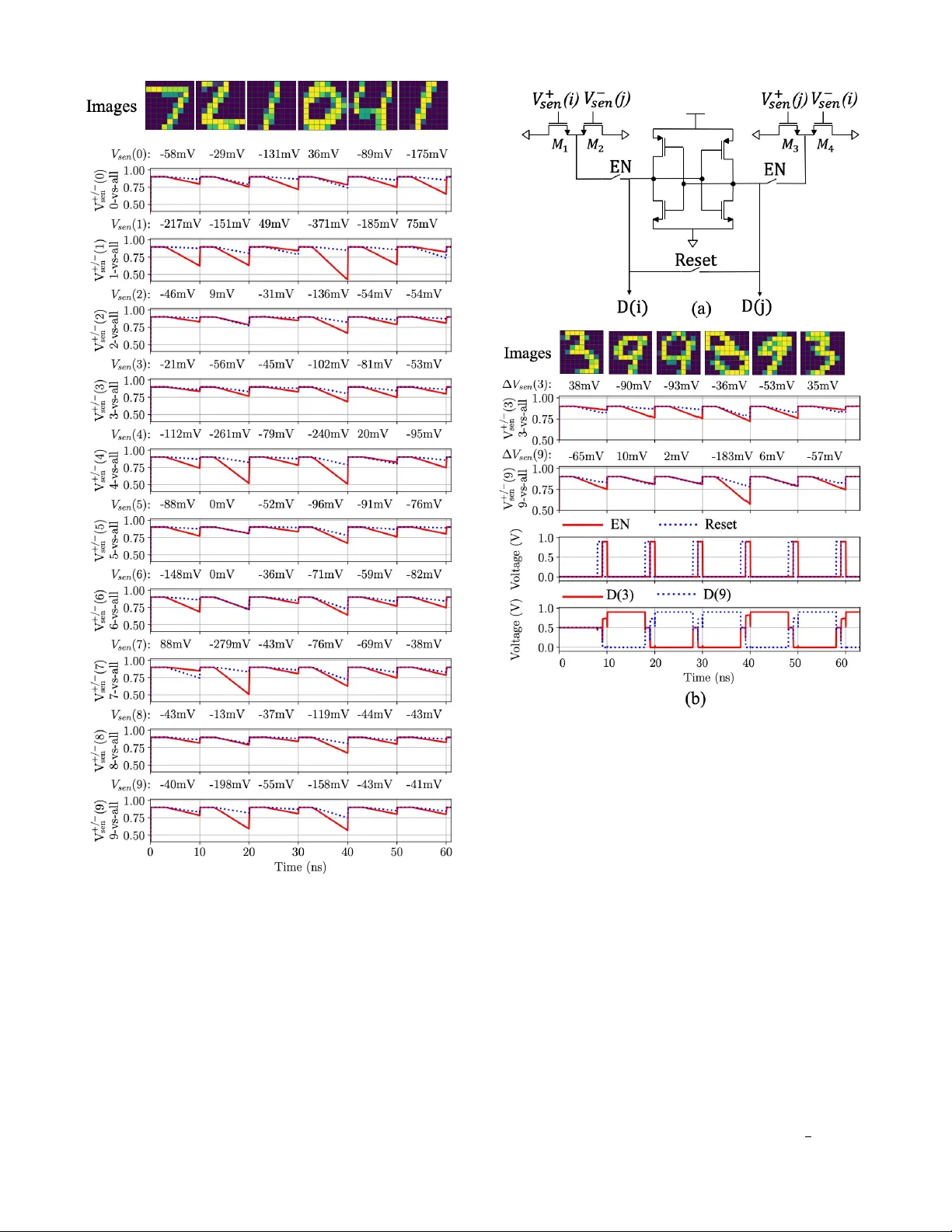

곱셈‑누적(MAC) 연산은 양·음 라인에 연결된 MOSFET들의 전류를 센싱 라인에 연결된 커패시터(Csen)로 적분해 전압 강하 형태로 구현한다. 서브스레시홀드 영역에서 동작하도록 바이어스함으로써 전류를 최소화하고, 9×9(81) 피처를 가진 MNIST 데이터셋에 대해 50 fF의 작은 커패시터만으로 충분히 동작한다. 서브스레시홀드 전류는 바디와 게이트 전압에 대해 지수적으로 변하므로, 학습 단계에서 피처에 제곱근 변환(√x)과 가중치에 로그 변환(ln w)을 적용해 비선형성을 보정한다. 이를 통해 회로 수준에서 선형 모델(로지스틱 회귀)의 출력과 일치하도록 설계하였다.

다중 클래스 분류는 One‑Versus‑All(OVA) 방식을 채택한다. K개의 클래스에 대해 각각 하나의 바이너리 분류기를 배치하면, 전체 트랜지스터 수는 K·N(여기서 N은 피처 수)으로, OVO 방식에 비해 선형적으로 증가한다. 각 바이너리 분류기의 출력 전압 차(ΔV⁺‑sen – ΔV⁻‑sen)는 해당 클래스의 신뢰도 점수 p_i 로 해석된다. 최종 결정은 가장 큰 p_i 를 가진 클래스로 선택하고, 차등 신뢰도 값을 이용해 경계가 모호한 경우를 식별한다. 이를 위해 저전력 비교기 회로를 설계해 전압 차를 빠르게 판단한다.

공정 측면에서는 트리플‑웰 구조를 사용해 개별 MOSFET 바디를 독립적으로 바이어스한다. 트리플‑웰은 바디 전압을 개별적으로 제어할 수 있어, 다수의 MOSFET이 동시에 다른 피처 값을 나타낼 때 필요한 전압 레벨을 제공한다. 그러나 트리플‑웰 레이아웃은 트윈‑웰 대비 면적이 약 3배 증가한다는 단점이 있다. 논문은 45 nm CMOS 기술을 기반으로 전체 면적을 2,179 µm², 전력 소모를 6.2 pJ·결정⁻¹로 구현했으며, 이는 최신 혼합‑신호 분류기 대비 각각 7.3배·45배 이상의 효율 향상을 의미한다.

실험에서는 MNIST 데이터셋을 9×9로 다운샘플링해 81개의 피처만 사용했으며, 로지스틱 회귀 기반 학습으로 90 % 정확도를 달성했다. SPICE 시뮬레이션을 통해 PVT(공정·전압·온도) 변동에 대한 견고성을 검증했으며, 전압 차 기반 신뢰도 추출이 정확도 저하 없이 안정적인 의사결정을 가능하게 함을 보였다.

본 연구의 주요 기여는 (1) 단일 MOSFET을 이용한 고해상도 곱셈 구현, (2) 서브스레시홀드 선형화 학습 흐름, (3) OVA 기반 신뢰도 주도 다중 클래스 결정, (4) 트리플‑웰 공정을 통한 바디 바이어스 독립 제어, (5) 기존 혼합‑신호 분류기에 비해 전력·면적·정확도 면에서 종합적인 우수성 입증이다. 한계점으로는 선형 모델에 국한된 적용 범위, 서브스레시홀드 동작 시 온도·공정 민감도, 피처 수 증가 시 센싱 캐패시터와 라인 저항에 의한 스케일링 제약이 있다. 향후 비선형 모델 확장, 자동 보정 회로 도입, 고밀도 트리플‑웰 레이아웃 최적화 등을 통해 실용성을 더욱 높일 수 있을 것으로 기대된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기