비대칭 소자에서도 신경망 학습을 가능하게 하는 티키타카 알고리즘

초록

이 논문은 저항성 교차점 배열을 이용한 아날로그 신경망 가속기에서 발생하는 소자 비대칭 문제를 해결하기 위해 “티키타카(Tiki‑Taka)” 알고리즘을 제안한다. 기존 SGD‑BP는 소자의 양·음 펄스에 대한 대칭 전도 변화가 전제되어 있었지만, 티키타카는 비대칭 전도 변화를 자동으로 보정하는 동적 커플링 시스템을 도입한다. 시뮬레이션 결과, 완전 연결, 합성곱, LSTM 등 다양한 네트워크 구조에서 비대칭 소자를 사용해도 대칭 이상적인 소자와 동일한 학습 정확도를 달성했으며, 연산은 여전히 배열 수준에서 병렬 처리되어 전력·속도 이점을 유지한다.

상세 분석

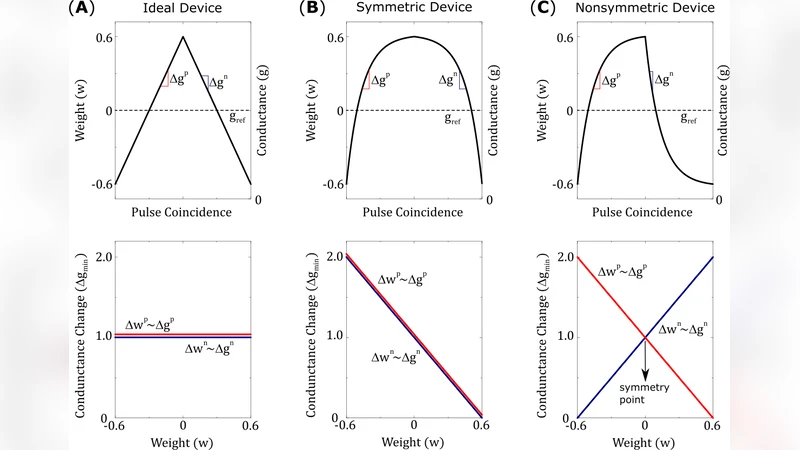

본 논문은 저항성 교차점(RRAM) 배열 기반 아날로그 가속기가 딥러닝 학습에 적용될 때 가장 큰 제약으로 작용하는 ‘소자 비대칭(symmetry)’ 문제를 근본적으로 재구성한다. 기존의 SGD‑BP 알고리즘은 가중치 업데이트를 전압 펄스로 구현하는데, 이때 양(positive) 펄스와 음(negative) 펄스가 동일한 크기의 전도 변화 ΔG를 일으켜야만 수학적 그래디언트와 물리적 업데이트가 일치한다. 실제 소자는 제조 공정, 재료 특성, 온도 등에 따라 ΔG⁺≠ΔG⁻인 비대칭을 보이며, 이는 SGD 식에 암묵적인 추가 비용(cost) 항을 삽입해 학습 수렴을 방해한다. 논문은 이 비대칭 비용을 ‘implicit regularization term’으로 모델링하고, 기존 SGD가 최소화하려는 손실 L(θ)와 별도로 발생하는 비용 C(θ) 를 동시에 최소화하는 새로운 동적 시스템을 설계한다.

티키타카 알고리즘은 두 개의 상호 연결된 업데이트 루프를 도입한다. 첫 번째 루프는 전통적인 손실 기반 그라디언트를 계산해 가중치를 업데이트하고, 두 번째 루프는 현재 가중치와 소자 비대칭 매핑을 이용해 C(θ)를 추정·보정한다. 두 루프는 시간 스케일을 달리하면서 서로 피드백을 주고받아, 비대칭으로 인한 편향이 점진적으로 상쇄되도록 설계된다. 수학적으로는

θ_{t+1}=θ_t−η∇L(θ_t)−γ∇C(θ_t)

와 같은 형태로 표현되며, η와 γ는 각각 학습률과 비대칭 보정률이다. 여기서 ∇C는 소자 특성을 사전 측정하거나 온라인으로 추정한 비대칭 파라미터를 기반으로 계산된다. 중요한 점은 이 보정 연산이 배열 내부에서 병렬적으로 수행될 수 있다는 점이다. 즉, 각 교차점은 자체적인 비대칭 파라미터를 저장하고, 로컬 연산만으로 ∇C를 구해 가중치 업데이트에 바로 적용한다. 따라서 추가적인 메모리 이동이나 시리얼 연산이 거의 필요하지 않다.

실험에서는 MNIST, CIFAR‑10, PTB 등 다양한 데이터셋과 네트워크 구조(FC, CNN, LSTM)를 대상으로, 이상적인 대칭 소자와 비대칭 소자를 각각 0.1%~1% 수준의 비대칭을 갖도록 설정했다. 티키타카를 적용한 경우, 비대칭 소자에서도 대칭 소자와 동일한 최종 정확도와 수렴 속도를 보였으며, 오히려 비대칭 보정 과정에서 발생하는 작은 정규화 효과가 과적합을 억제하는 부수 효과를 제공하기도 했다. 전력 소모와 연산 지연 측면에서도 기존 배열‑기반 SGD와 거의 차이가 없으며, 추가적인 보정 회로가 최소화된 설계 덕분에 전체 시스템 효율성을 유지한다.

이러한 결과는 저항성 소자의 물리적 한계를 알고리즘 차원에서 완화함으로써, 소재 연구와 공정 비용을 크게 낮출 수 있음을 시사한다. 비대칭을 허용하면서도 학습 정확도를 유지하는 티키타카 알고리즘은 차세대 아날로그 딥러닝 가속기의 실용화를 앞당기는 핵심 기술로 평가될 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기