자원 효율적인 임베디드 아이리스 인식 시스템: 경량 FCN과 FPGA 가속

본 논문은 아이리스 인식 파이프라인에 FCN 기반 세분화를 도입하고, 3단계 SW/HW 공동 설계(아키텍처 탐색, 8‑bit 동적 고정소수점 양자화, FPGA 가속)를 통해 연산량을 50배 감소시키면서도 최고 수준의 세분화·인식 정확도를 달성한다. 최종 시스템은 임베디드 CPU 대비 최대 8.3배 빠른 처리 속도를 보이며, FPGA 자원 사용률은 15% 이하이다.

저자: Hokchhay Tann, Heng Zhao, Sherief Reda

본 논문은 아이리스 인식 시스템을 모바일·임베디드 환경에 적용하기 위해, 기존의 고성능이지만 연산량이 방대한 Fully Convolutional Network(FCN) 기반 세분화 모델을 경량화하고 하드웨어 가속을 결합한 종합 솔루션을 제시한다.

1. **연구 배경 및 문제 정의**

아이리스는 변형이 거의 없고 고유한 패턴을 가지고 있어 바이오메트릭 인증에 이상적이다. 전통적인 파이프라인은 전처리, 원형 허프 변환·적분 미분 연산 기반 세분화, 고무 시트 모델을 통한 정규화, 로그 가보르 필터 기반 인코딩 순으로 진행된다. 특히 세분화와 전처리 단계가 연산 집약적이며, 기존 딥러닝 기반 세분화 모델은 수십억 FLOPs를 요구해 임베디드 시스템에 부적합했다.

2. **제안된 엔드‑투‑엔드 파이프라인**

- **FCN 기반 세분화**: Encoder‑Decoder 구조에 skip connection을 적용한 경량 FCN을 설계한다.

- **컨투어 피팅**: FCN이 출력한 바이너리 마스크에서 가장 큰 연결 객체의 중심과 장·단축축을 이용해 대략적인 원 중심·반경을 추정하고, 이를 초기값으로 원형 허프 변환을 재적용해 정밀한 아이리스·동공 경계를 구한다.

- **정규화·인코딩**: Daugman의 고무 시트 모델과 1‑D 로그 가보르 필터를 그대로 사용해 정규화된 원통형 이미지와 바이너리 코드(iris code)를 생성한다.

3. **SW/HW 공동 설계 3단계 방법론**

- **아키텍처 탐색**: 레이어 수, 채널 수, 다운샘플링 비율 등을 다양하게 조합해 10여 개의 후보 모델을 생성하고, 각 모델을 전체 파이프라인에 적용해 인증 정확도(EER)와 연산량을 동시에 평가한다. 가장 효율적인 모델은 기존 최고 성능 모델 대비 50배 적은 FLOPs를 보이며, 세분화 F‑measure는 0.96 수준을 유지한다.

- **정밀도 양자화**: 가중치·활성값을 8‑bit 동적 고정소수점(DFP)으로 양자화한다. 각 레이어별 스케일 팩터를 학습 단계에서 추정해 정밀도 손실을 최소화하고, 양자화 후에도 세분화 정확도는 0.2% 이하로 감소한다.

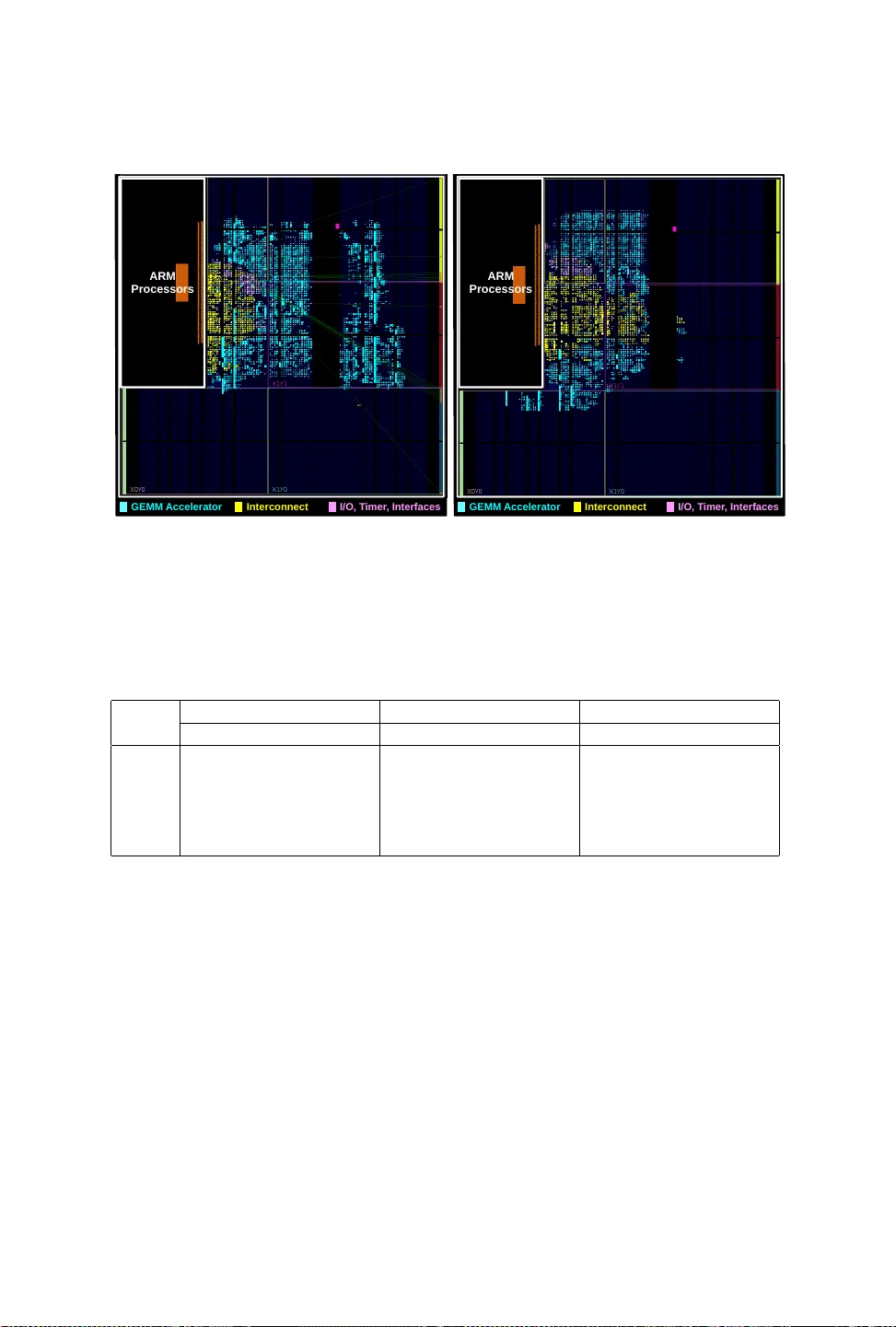

- **하드웨어 가속기 설계**: Xilinx FPGA(예: Zynq‑7000) 위에 DFP 전용 MAC 유닛을 다중 파이프라인 형태로 구현한다. 데이터 재사용을 위해 라인 버퍼와 블록 RAM을 활용하고, 연산 스케줄러를 설계해 레이턴시를 최소화한다. 부동소수점 버전도 동일 구조로 구현해 비교한다.

4. **실험 설정 및 결과**

- **데이터셋**: IRISSEG‑EP와 상용 NIR 아이리스 데이터셋 두 개를 사용해 세분화(F‑measure, Precision, Recall)와 전체 인증률(EER)을 측정한다.

- **성능**: 제안된 경량 FCN+가속기 파이프라인은 기존 최첨단 방법보다 1~2% 높은 인증 정확도를 기록했으며, 특히 눈꺼풀·반사에 의해 손상된 이미지에서도 강인성을 보였다.

- **속도·자원**: FPGA 구현은 전체 파이프라인에서 평균 8.3배 가속을 달성했으며, LUT 12%, FF 9%, DSP 13% 사용으로 FPGA 용량의 15% 이하에 머물렀다. 임베디드 CPU 대비 8배 빠른 처리 속도와 전력 효율을 제공한다.

- **GPU 비교**: 동일 모델을 Jetson 같은 임베디드 GPU에 배치했을 때는 처리량이 높지만 전력 소모와 메모리 요구량이 크게 증가한다는 점을 확인했다.

5. **논의 및 의의**

- **전체 파이프라인 관점**: 세분화 정확도만을 최적화하는 것이 전체 인증 성능을 보장하지 않음을 실험적으로 입증하고, 엔드‑투‑엔드 평가가 필수임을 강조한다.

- **양자화와 가속기의 시너지**: 8‑bit DFP 양자화가 연산량을 크게 줄이고, FPGA 가속기가 이를 효율적으로 처리함으로써 실시간 인증이 가능한 시스템을 구현했다.

- **실용성**: 모바일·웨어러블 디바이스에 적용 가능한 저전력·저지연 아이리스 인증 솔루션으로, 보안·프라이버시 요구가 높은 응용 분야(스마트폰, 스마트 안경, 차량 인증 등)에 바로 활용 가능하다.

6. **결론**

본 연구는 FCN 기반 아이리스 세분화와 맞춤형 FPGA 가속기를 결합한 자원 효율적인 임베디드 아이리스 인식 시스템을 제시한다. 3단계 SW/HW 공동 설계 방법론을 통해 연산량을 50배 감소시키면서도 최고 수준의 세분화·인식 정확도를 유지했으며, 실제 FPGA 보드에서 8.3배 가속과 15% 이하 자원 사용을 달성했다. 이는 차세대 바이오메트릭 디바이스에 실시간, 고보안 아이리스 인증을 제공할 수 있는 중요한 기술적 토대를 마련한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기