256채널 TOF 전자시스템으로 중성자 빔 프로파일링 구현

본 논문은 중국 스플리션 중성자원(CSNS) “Back‑n WNS” 빔라인에서 사용되는 256채널 시간비행(TOF) 전자시스템을 설계·구현하고, 3.5 ns 이하의 시간 정밀도와 10 ms 동적 범위를 달성한 실험 결과를 보고한다. 전면부(FEB)와 4개의 TDC 보드, 클럭 분배 모듈(CDM)로 구성된 시스템 구조와 각 부품의 회로 설계, FPGA 기반 위상 분리 기법을 통한 시간 측정 원리를 상세히 설명한다.

저자: Haolei Chen, Changqing Feng, Jiadong Hu

본 논문은 중국 스플리션 중성자원(CSNS) 내 “Back‑n WNS” 빔라인에서 중성자 에너지 분해능을 확보하기 위한 256채널 시간비행(TOF) 전자시스템을 설계·구현하고, 실험 검증 결과를 제시한다. 서론에서는 백‑엔 스트리밍 중성자 빔이 eV부터 수백 MeV까지 넓은 에너지 스펙트럼을 갖고 있기에, 에너지 해상도 1 % 이하(10 MeV에서 ≈9 ns 시간 정밀도)를 달성하기 위한 TOF 측정 필요성을 강조한다. 기존 BES III·AMS‑02 시스템은 HPTDC ASIC을 사용해 25 ps~265 ps 수준의 정밀도를 제공하지만, 채널 수와 비용, 설계 유연성에서 제한이 있다.

시스템 구성은 크게 전면부(FEB), 4개의 TDC 보드, 클럭 분배 모듈(CDM), 그리고 PXI 크레이트 기반 컨트롤 보드로 나뉜다. FEB는 256채널 PMT(H9500)에서 발생한 -0.8 ns 상승시간의 전류 펄스를 전압으로 변환하고, LMH6722(4채널) 증폭기로 2 V/V 이득을 부여한다. 이후 AD8564(4채널) 비교기로 -5 V~0 V 가변 임계값을 적용해 TTL 펄스로 디지털화하고, LVDS 차동 라인으로 변환해 2 m 케이블을 통해 TDC 보드에 전달한다. 이 설계는 고대역폭(400 MHz)과 저전력(±5 V) 동작을 동시에 만족한다.

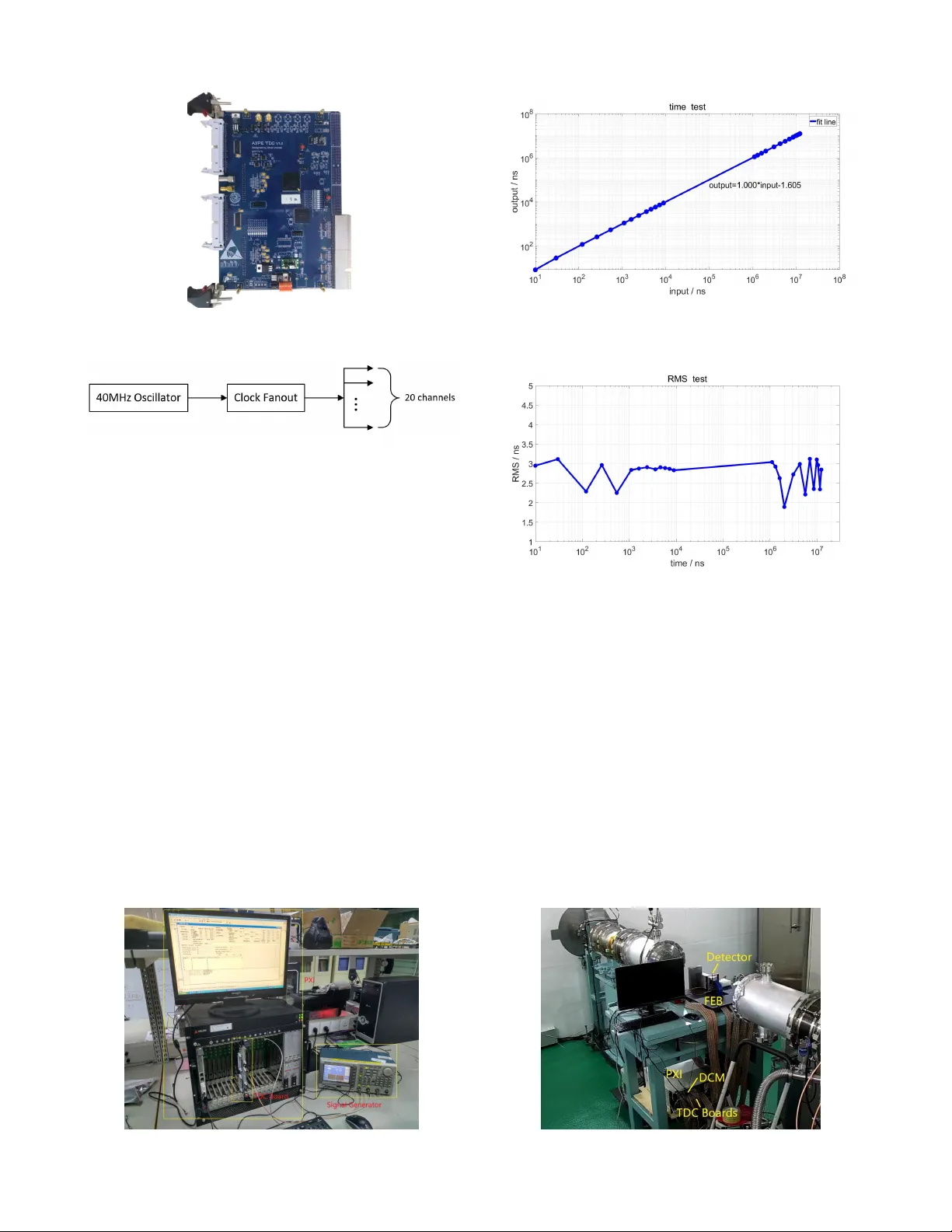

TDC 보드는 6U PXI 폼팩터이며, 각 보드당 64채널을 처리한다. FPGA 내부에 40 MHz 기준 클럭을 이용한 22‑bit 카운터와 위상 분리 회로(0°, 90°, 180°, 270°)를 배치해 기본 25 ns 해상도를 6.25 ns까지 향상시켰다. 시작 신호는 프로톤 빔 펄스이며, 정지 신호는 FEB에서 전달된 LVDS 펄스이다. FPGA는 시작 신호를 감지하면 정지 신호를 수신하고, 10 ms(≈100 ms)까지의 타임 윈도우를 지원한다. 두 채널씩 데이터를 FIFO에 임시 저장하고, 10 ms 후 새로운 정지 신호를 차단해 데이터 전송을 마친다.

CDM은 단일 고정밀 클럭 소스로부터 4개의 동기화된 클럭을 생성해 각 TDC 보드에 공급한다. 이를 통해 보드 간 타임 오프셋을 최소화하고, 전체 시스템의 동기성을 보장한다.

시스템 검증은 두 단계로 진행되었다. 첫 번째는 신호 발생기(AFG3252)를 이용한 TDC 보드 자체 테스트로, 시작·정지 펄스 간 간격을 가변시켜 선형성 및 정밀도를 측정하였다. 결과는 10 ms 동적 범위 내에서 RMS < 3.5 ns, 비선형 오차는 수십 ps 수준으로, 설계 목표를 충분히 초과함을 확인했다. 두 번째는 실제 CSNS 환경에서의 TOF 시스템 테스트이다. 30 mm 직경의 원형 스폿을 PMT에 투사해 히트맵과 시간 스펙트럼을 획득했으며, 얻어진 데이터는 중성자 공명 방사촬영 연구에 바로 활용될 수 있다.

결론에서는 256채널 FEB와 4개의 64채널 TDC 보드가 결합된 시스템이 3.5 ns 이하의 시간 정밀도와 10 ms 동적 범위를 제공함을 강조한다. ASIC 기반 HPTDC 대비 비용·유연성 측면에서 우수하며, 향후 고채널 수집 및 실시간 데이터 처리 요구에 맞춰 FPGA 펌웨어를 확장할 수 있는 가능성을 제시한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기