두 포트 네트워크 기반 피드백 회로 분석의 간소화된 접근법

초록

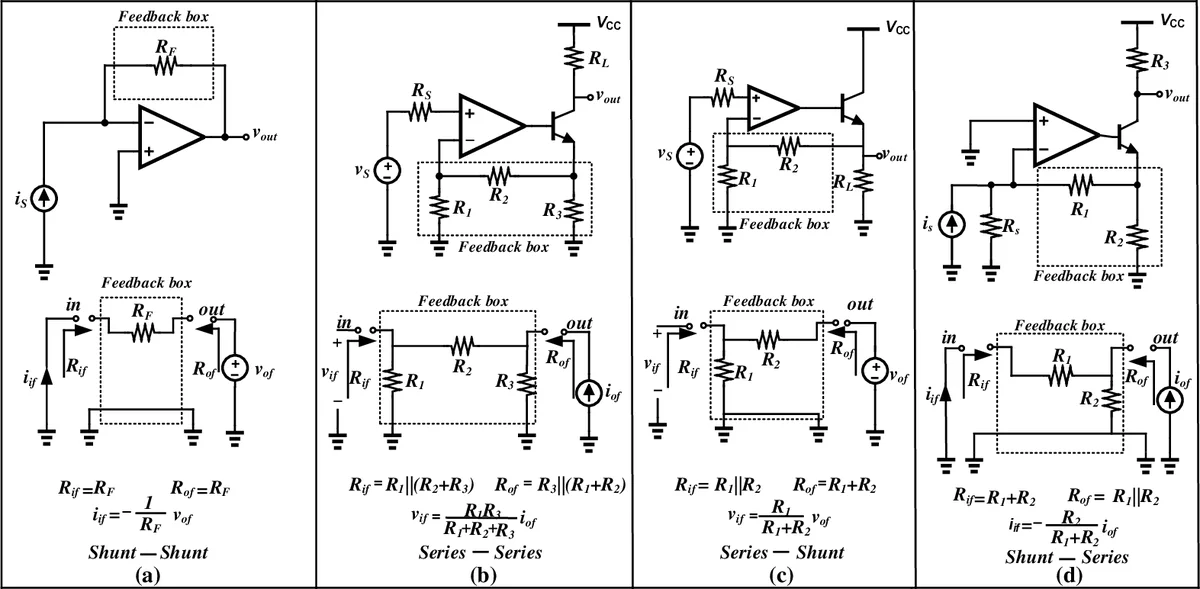

본 논문은 전통적인 두 포트 네트워크 이론을 재구성하여 피드백 회로, 특히 출력 전류를 감지하는 출력 직렬 피드백의 출력 임피던스를 직관적으로 계산하는 방법을 제시한다. 네 가지 기본 피드백 토폴로지를 시각화하고, 로딩 효과를 간단히 판단할 수 있는 규칙을 도입함으로써 학생들의 이해도를 높인다.

상세 분석

이 논문은 전통적인 KVL‑KCL, 신호 흐름 그래프(SFG), 반환비(Return‑Ratio) 등 기존 피드백 해석 기법이 초보 학습자에게 복잡하고 직관성을 결여한다는 점을 지적한다. 그 대안으로 두 포트 네트워크 모델을 활용한 교육용 접근법을 제시하는데, 핵심은 피드백 회로를 네 가지 기본 형태(시리즈‑시리즈, 시리즈‑샤운트, 샤운트‑시리즈, 샤운트‑샤운트) 중 하나에 매핑하고, 각 형태에 대응하는 Y, Z, h, g 파라미터를 기억할 필요 없이 회로 구조만으로 로딩 효과를 판단한다는 것이다.

특히 저자는 피드백 신호가 입력·출력 포트에 어떻게 연결되는지를 도식화한 Fig. 1·2를 통해 “피드백 유형 인식 → 피드백 회로 분리 → 전압·전류원으로 구동 → 로딩 효과 직관적 파악”이라는 4단계 절차를 제안한다. 이 과정에서 시리즈‑샤운트 피드백을 예시로 들어, 입력 측은 개방 회로, 출력 측은 단락 회로라는 전통적인 직관을 명확히 시각화한다.

논문의 가장 큰 기술적 기여는 출력 직렬 피드백(출력 전류 감지) 상황에서 출력 임피던스를 정확히 도출한 점이다. 기존 교과서에서는 출력 임피던스가 1 + T(루프 이득) 배 증가한다는 식만 제시하고, 실제 회로 구조에 따른 상세 계산을 제공하지 않는다. 저자는 먼저 전체 회로를 Thevenin 등가 회로(v_th = K·v_in, r_th = r_out)로 치환하고, 출력 브랜치를 R₁, r_out, r_π·β + 1 등으로 구성한다. 피드백이 추가되면 이 브랜치 저항이 (1 + a·f) 배로 확대되며, 이를 바탕으로 식 (3)·(9)‑(14)를 차례로 전개한다. 결과적으로 출력 임피던스는 R_X와 R₂의 병렬 결합으로 표현되며, R_X는 K·R₁·β + r_out + r_π·β 등으로 구체화된다.

또한 CMOS 설계에서 R₂가 전류원으로 대체되는 최신 트렌드와, 나노미터 MOSFET의 r_o 감소 현상을 고려해 기존 근사식이 부적합함을 지적하고, 제시된 정확한 식이 설계 단계에서 실질적인 가이드가 될 수 있음을 강조한다.

마지막으로 SFG와 KVL‑KCL을 이용해 제안된 식을 검증함으로써, 두 포트 기반 접근법이 수학적 정확성을 유지하면서도 교육적 직관성을 제공한다는 점을 입증한다. 전체적으로 이 논문은 피드백 회로 교육에 필요한 복잡성을 크게 낮추고, 특히 출력 직렬 피드백의 정확한 임피던스 해석을 제공함으로써 학습자와 설계자 모두에게 실용적인 도구를 제공한다.

댓글 및 학술 토론

Loading comments...

의견 남기기