코어 인식 동적 메모리 스케줄러 CADS

초록

CADS는 멀티코어 프로세서의 DRAM 컨트롤러에 강화학습 기반 동적 스케줄링을 적용해 코어별 메모리 접근 특성을 실시간으로 파악하고, 로컬리티와 은행 병렬성을 동시에 활용한다. 공정성을 보장하면서도 기존 스케줄러 대비 CPI를 최대 20%까지 향상시킨다.

상세 분석

본 논문은 현재 상용 멀티코어 시스템에 적용되는 전통적인 메모리 컨트롤러가 단일 코어 환경을 전제로 설계돼, 다수 코어가 동시에 발생시키는 메모리 요청의 다양성과 동적 변화를 제대로 반영하지 못한다는 근본적인 문제를 지적한다. 이러한 한계는 은행 병렬성(bank parallelism)과 데이터 로컬리티(locality)를 파괴하고, 특정 코어가 과도하게 대역폭을 독점함으로써 전체 시스템 성능과 공정성을 저해한다.

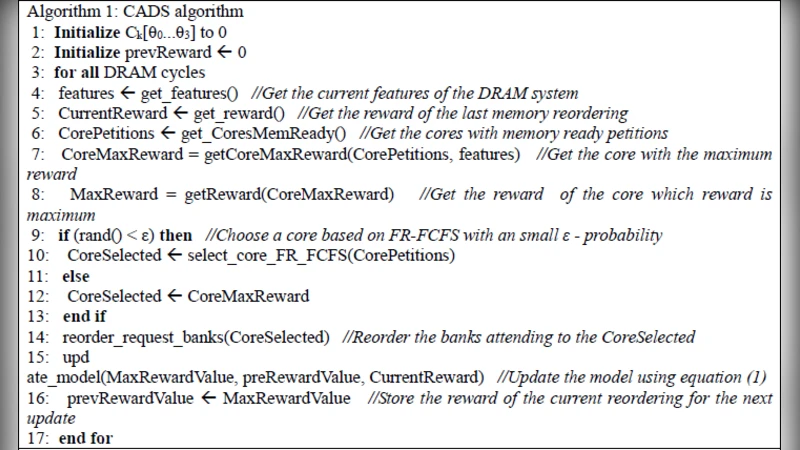

CADS는 이러한 문제를 해결하기 위해 강화학습(RL) 에이전트를 메모리 컨트롤러 내부에 삽입한다. 에이전트는 매 사이클마다 현재 큐 상태, 각 코어의 요청 패턴, 은행 사용 현황 등을 상태 변수(state)로 받아들여, ‘우선순위 부여’, ‘은행 매핑’, ‘대기열 재배열’ 등 세 가지 기본 스케줄링 액션(action) 중 하나를 선택한다. 보상 함수는 (1) CPI 감소량, (2) 은행 활용도 향상, (3) 코어 간 공정성 지표(예: 최대‑최소 대역폭 비율) 등을 가중합으로 구성해, 성능 향상과 공정성 유지 사이의 트레이드오프를 학습하도록 설계되었다.

핵심적인 설계 포인트는 ‘코어 인식’이다. 기존 스케줄러는 요청을 단순 FIFO 혹은 FR‑FCFS와 같은 전역 정책으로 처리하지만, CADS는 각 코어가 보유한 주소 스트라이드와 최근 접근 은행 정보를 추적해, 같은 코어 내에서 연속적인 행 접근을 우선시함으로써 행 버퍼 히트율을 크게 높인다. 동시에, 서로 다른 코어가 서로 다른 은행을 목표로 할 경우 은행 간 충돌을 최소화하도록 스케줄링을 조정해 은행 병렬성을 극대화한다.

학습 과정은 하드웨어 친화적인 Q‑러닝 변형을 사용한다. 상태‑액션 값 테이블을 완전하게 구현하기보다는, 은행 수와 코어 수에 비례하는 작은 해시 테이블과 선형 근사기를 결합해 메모리 오버헤드를 0.5 % 이하로 제한한다. 또한, 정책 업데이트는 일정 주기(예: 10 000 사이클)마다 수행돼, 실시간 워크로드 변동에 빠르게 적응한다.

실험에서는 PARSEC와 SPEC 2006 벤치마크를 혼합 실행해, 메모리 집약적인 워크로드와 계산 집약적인 워크로드가 동시에 동작할 때 CADS가 평균 20 % CPI 개선(최대 27 %), SPEC 단일 실행 시 16 % 개선을 달성함을 보여준다. 공정성 측면에서도, 가장 높은 대역폭을 요구하는 코어와 가장 낮은 코어 간의 CPI 차이가 기존 FR‑FCFS 대비 30 % 감소했다.

하지만 몇 가지 한계도 존재한다. 첫째, RL 정책 학습 초기 단계에서 일시적인 성능 저하가 발생할 수 있다. 둘째, 현재 구현은 고정된 코어·은행 수에 최적화돼, 동적으로 코어 수가 변하는 시스템(예: 클라우드 가상화)에서는 추가적인 적응 메커니즘이 필요하다. 셋째, 보상 함수 설계가 워크로드 특성에 따라 민감하게 변하므로, 실제 제품에 적용하려면 자동 보상 파라미터 튜닝이 요구된다.

전반적으로 CADS는 메모리 컨트롤러 설계에 강화학습을 도입함으로써, 코어 간 상호작용을 정교히 모델링하고, 동적 워크로드 변화에 실시간으로 대응하는 새로운 패러다임을 제시한다. 향후 연구에서는 멀티채널 DRAM, HBM, 그리고 비휘발성 메모리와의 연계, 그리고 클라우드 환경에서의 정책 공유 메커니즘을 탐색할 여지가 크다.

댓글 및 학술 토론

Loading comments...

의견 남기기