광학 기반 컨볼루션 신경망 가속기 PCNNA 설계와 성능 분석

본 논문은 실리콘 포토닉 마이크로링 가중치 뱅크와 broadcast‑and‑weight 프로토콜을 활용해 CNN의 컨볼루션 연산을 광학적으로 가속하는 PCNNA 구조를 제안한다. 입력 피처맵과 커널 사이의 희소 연결성을 이용해 필요 마이크로링 수를 크게 줄이고, 단일 광학 코어를 여러 레이어에 순차적으로 재사용함으로써 면적·전력 효율을 높인다. 분석 결과, 광학 코어만 고려했을 때 전자식 대비 최대 5 order의 속도 향상이 가능하며, 전체 …

저자: Armin Mehrabian, Yousra Al-Kabani, Volker J Sorger

본 논문은 실리콘 포토닉 기술을 활용한 컨볼루션 신경망 가속기인 PCNNA(Photonic Convolutional Neural Network Accelerator)를 제안한다. 기존 전자식 가속기들은 컨볼루션 연산이 전체 연산량의 90%를 차지한다는 점에서 전력·속도 한계에 직면해 있다. 포토닉 시스템은 높은 대역폭, 낮은 전력 소비, 그리고 파장 분할 다중화(WDM)를 통한 본질적인 병렬성을 제공한다는 장점을 갖는다. 저자들은 이러한 포토닉의 특성을 CNN의 구조적 특성, 즉 입력 피처맵과 커널 사이의 희소 연결성에 결합한다.

핵심 기술은 마이크로링 공진기(MRR) 기반 가중치 뱅크와 broadcast‑and‑weight 프로토콜이다. 각 뉴런 출력은 서로 다른 파장(LD)으로 변조되어 웨이브가이드에 다중 파장으로 전송되고, 목적지 레이어에서는 MRR이 각 파장의 진폭을 가중치에 따라 조절한다. 포토다이오드가 모든 파장을 합산해 전류 형태의 MAC 결과를 생성한다. 이 과정은 광학적으로 거의 즉시(광 전파 시간) 수행되며, 5 GHz의 빠른 클럭 도메인 안에서 한 사이클에 완료된다.

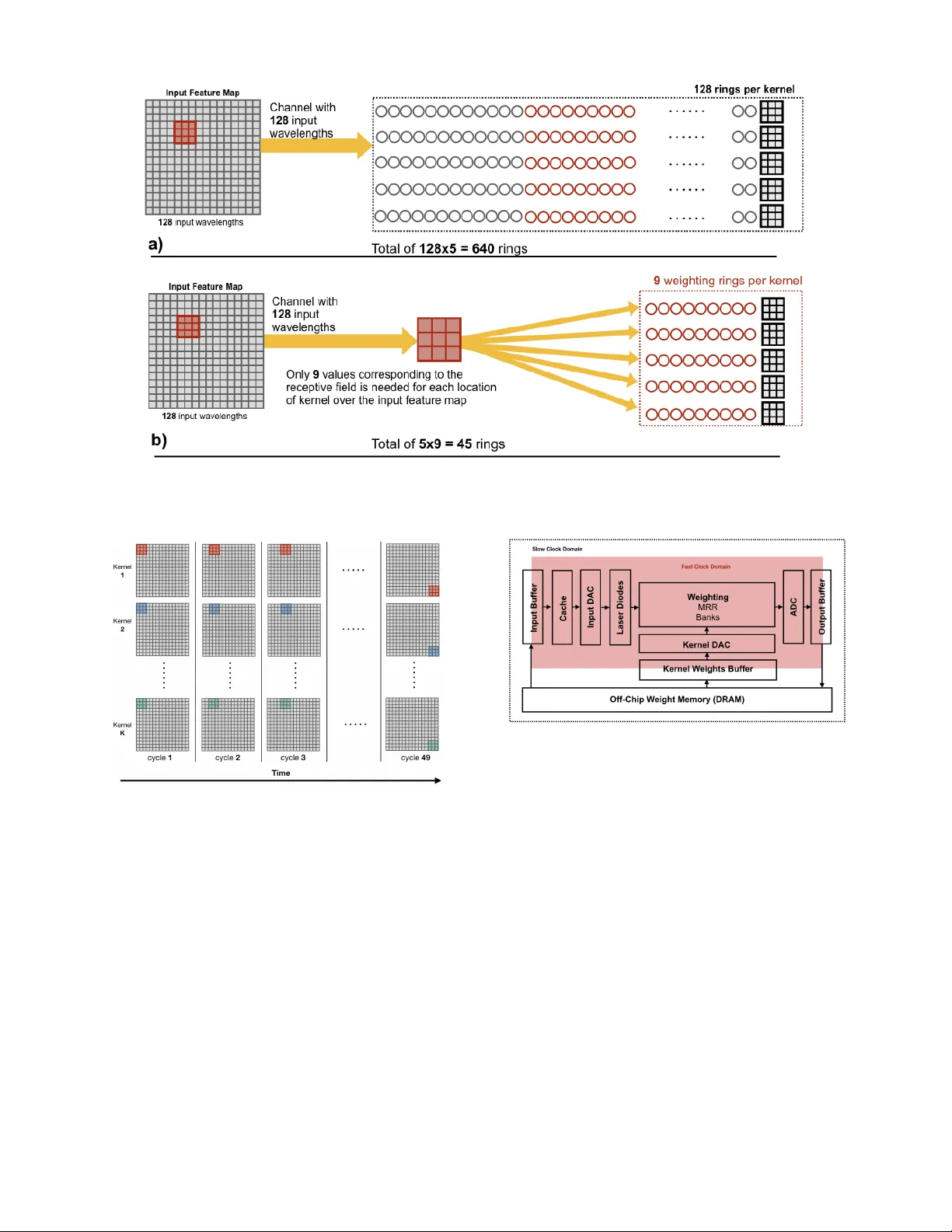

하지만 MRR 수가 입력 피처맵 크기와 커널 수에 비례해 기하급수적으로 증가하면 실현이 불가능하다. 저자들은 “비수용 영역 값 필터링”을 도입해 실제 연산에 필요한 입력 값(N_kernel)만을 MRR에 연결한다. 이를 통해 전체 마이크로링 수가 N_input × K × N_kernel에서 K × N_kernel으로 감소한다. 예시로 AlexNet 1층(224 × 224 × 3 입력, 96개 11 × 11 × 3 커널)의 경우, 필터링 전 5.2 B개의 마이크로링이 필요하지만 필터링 후 35 k개만 필요하게 된다. 이는 면적(≈2.2 mm²)과 전력 소모를 크게 절감한다.

PCNNA는 전체 CNN을 하나의 광학 코어에 순차적으로 매핑한다. 레이어가 바뀔 때마다 가중치는 오프‑칩 DRAM에서 로드되어 전자‑아날로그 변환(DAC) 후 MRR에 적용된다. 입력 피처맵은 DRAM에서 SRAM 캐시로 전송되고, DAC를 통해 아날로그 신호로 변환된다. 하나의 수용 영역에 대해 K개의 커널이 동시에 처리되며, 광학 코어는 5 GHz 클럭 하나로 모든 MAC 연산을 수행한다. 따라서 전체 컨볼루션 시간 T_conv은 입력 위치 수(N_locs)와 1/f_clock의 곱으로 계산되며, 커널 수에 독립적이다.

실제 시스템 성능은 전자‑광 인터페이스, 특히 DAC의 변환 속도에 의해 제한된다. 저자는 6 GS/s DAC를 사용하고, 한 위치당 업데이트되는 입력 값 수를 고려해 최대 116번의 DAC 연산이 필요함을 보인다. 이 전자‑광 병목을 포함한 전체 시스템(PCNNA(O+E))에서도, Eyeriss와 YodaNN 같은 최신 전자식 가속기 대비 3 order 이상의 실행 시간 감소가 예상된다. 광학 코어만 고려했을 때(PCNNA(O))는 최대 5 order의 속도 향상이 가능하다.

논문은 마이크로링 면적(25 µm × 25 µm), DAC/ADC 사양(6 GS/s, 2.8 GS/s), SRAM 용량(128 kB) 등을 기반으로 면적·전력·속도 모델을 제시한다. 결과적으로 PCNNA는 현재 포토닉 공정 기술과 호환되며, 대규모 CNN에도 적용 가능함을 시뮬레이션으로 입증한다. 다만, 광학 코어와 전자 회로 간 데이터 이동, 온도·공정 변동에 따른 MRR 튜닝 정확도, DAC/ADC 해상도와 전력 효율 등 실용화에 필요한 과제가 남아 있다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기