광학 측정을 위한 개방형 고유연성 디지털 위상 고정 루프

본 논문은 저가의 Red Pitaya FPGA 보드를 기반으로 한 오픈소스 디지털 위상 고정 루프(DPLL)를 설계·구현하고, 이를 400 m 광섬유 노이즈 취소 시스템에 적용해 30 kHz 대역폭의 위상 잡음 억제를 실증한다. 플랫폼 전체 지연은 565 ns이며, 이론적으로 225 kHz까지 제어 대역폭을 확보할 수 있다.

저자: Alex Tourigny-Plante, Vincent Michaud-Belleau, Nicolas Bourbeau-Hebert

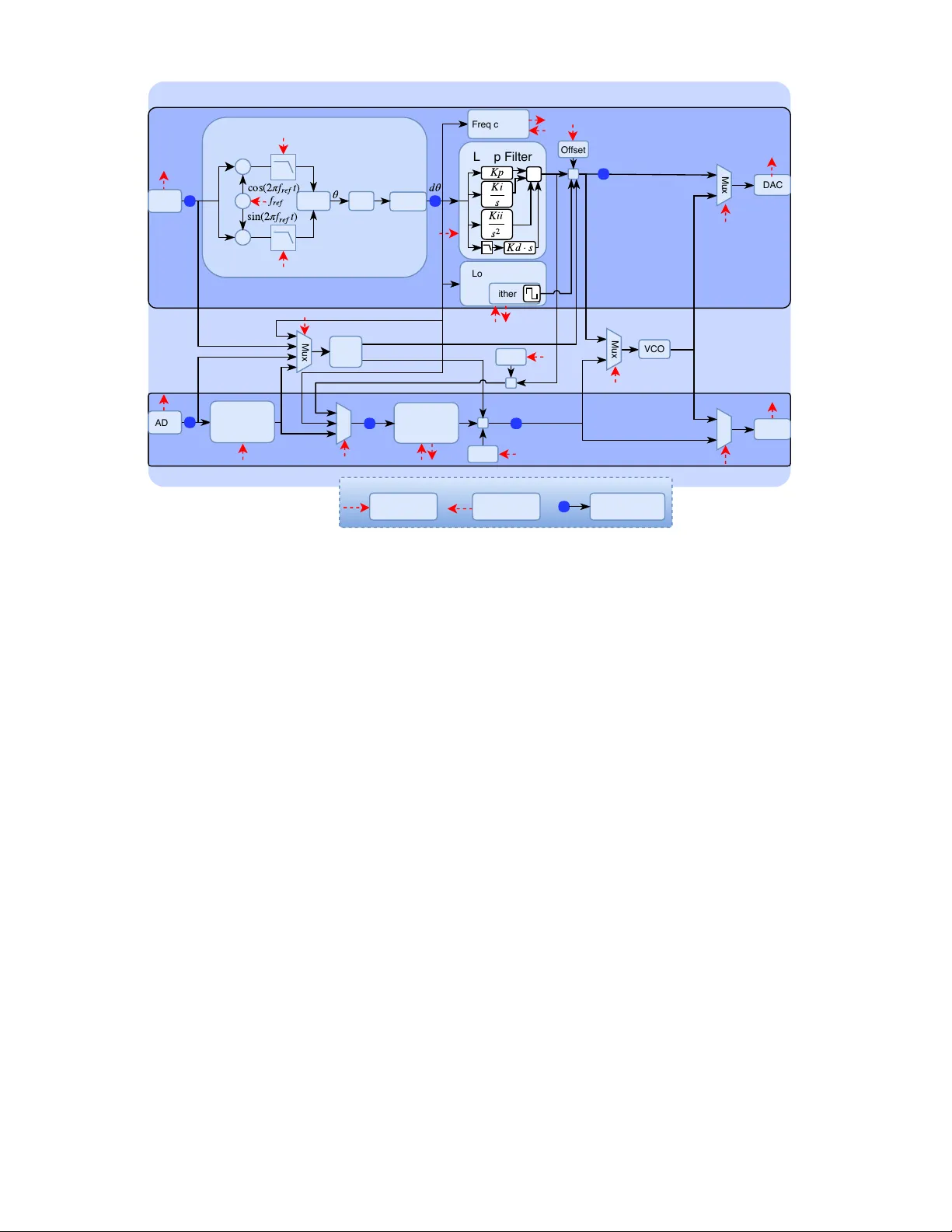

본 논문은 광학 메트로노미와 레이저 주파수 안정화에 필수적인 디지털 위상 고정 루프(DPLL)를 저비용 FPGA 보드인 Red Pitaya를 기반으로 구현하고, 이를 실제 광섬유 노이즈 취소 시스템에 적용한 전 과정을 상세히 기술한다. 먼저, 기존 디지털 서보 시스템이 제공하는 소프트웨어 재구성 가능성, 복제 용이성, 고급 진단 도구 등의 장점을 소개하고, 이러한 장점이 광학 분야에서 아직 충분히 활용되지 못한 이유(복잡한 하드웨어 설계, 높은 비용)를 지적한다. 이를 해결하기 위해, 저자들은 Red Pitaya 보드에 맞춤형 오픈소스 펌웨어와 파이썬 기반 GUI를 개발하였다. 보드는 Xilinx Zynq‑7010 FPGA와 14‑bit ADC/DAC를 탑재하고 있으며, 125 MHz 클럭으로 동작한다. 각 채널은 ADC를 통해 입력 신호를 디지털화하고, 사전에 정의된 48‑bit 분수 형태의 기준 주파수와 곱해 I/Q 성분을 얻는다. 디지털 저역통과 필터(3.75, 15.5, 31 MHz 중 선택) 후, arctan 연산으로 위상 오차를 추출하고, 위상 차분을 통해 위상 램프의 무한 증가 문제를 해결한다.

위상 오차는 PII²D(비례·적분·이중 적분·미분) 제어기로 전달된다. 비례 이득은 오픈루프 DC 이득(kc)에 대한 dB 비율로 설정되며, 적분·이중 적분·미분 항은 각각 교차 주파수(fi, fii, fd)로 정의된다. 이 설계는 수치 미분·적분이 샘플링 주파수(fs)에 비례하도록 보정함으로써, 디지털 구현 시 발생할 수 있는 스케일링 오류를 방지한다. 또한, 이중 적분 항은 정적 오프셋을 완전히 제거하고, 미분 항은 고주파 잡음 억제에 기여한다.

보드에는 내부 전압 제어 발진기(VCO)가 포함되어 있어, 0 ~ 62.5 MHz 범위의 주파수를 직접 생성한다. VCO는 16‑bit DDS를 통해 제어되며, 출력에 dither 신호(정현파 또는 사각파)를 추가해 시스템 전반의 전달 함수를 실시간으로 측정할 수 있다. 내장된 VNA 모듈은 주파수 응답을 자동으로 캘리브레이션하고, GUI를 통해 위상·주파수 잡음 PSD, 통합 위상 잡음 등을 실시간으로 시각화한다. 또한, 1 s 게이트 타임을 갖는 제로 데드타임 주파수 카운터가 장착되어 장기 안정성을 모니터링한다.

플랫폼은 세 가지 제어 시나리오를 지원한다. 첫째, 두 채널이 독립적으로 각각 ADC·루프·DAC를 사용해 별도 시스템을 제어한다(예: 주파수 콤보 레퍼런스). 둘째, 두 채널이 동일 ADC와 디모듈레이션 블록을 공유해 같은 입력에 대해 서로 다른 루프 필터를 적용한다(예: 빠른 피에조와 느린 피에조를 병행 제어). 셋째, 첫 번째 채널의 출력을 두 번째 채널의 입력으로 피드백해 다중 액추에이터를 연계한다(예: 느린 액추에이터로 빠른 액추에이터의 동작 범위 유지).

실험에서는 400 m 광섬유 링크에 대한 노이즈 취소를 구현하였다. 레이저 빔은 AOM(27 MHz)으로 주파수 변조되고, 반사된 빔이 로컬 사이트로 돌아와 위상 차이를 측정한다. DPLL은 54 MHz 기준 주파수로 I/Q 디모듈레이션을 수행하고, 위상 오차를 VCO에 피드백한다. AOM의 전달 함수는 VNA를 통해 측정했으며, 약 1.5 µs의 지연을 보였다. 광섬유 자체의 왕복 지연은 2 µs, FPGA 내부 지연은 0.5 µs로 총 4 µs가 된다. 이론적으로는 1/(8·τ)≈31 kHz의 대역폭이 제한되지만, 실제 실험에서는 30 kHz 대역폭을 달성하였다. 플랫폼 자체의 지연은 565 ns(ADC·DSP·DAC·VCO 포함)이며, 이는 이론적으로 225 kHz까지의 제어 대역폭을 가능하게 한다.

마지막으로, 저자들은 Red Pitaya 기반 DPLL이 상용 아날로그 락 박스 대비 수백 배 저렴하면서도, 오픈소스 펌웨어와 파이썬 GUI를 통해 재현성·확장성을 크게 향상시킨다고 결론짓는다. 또한, FPGA 내부에서 직접 위상 추출·루프 연산을 수행함으로써 아날로그-디지털 변환 단계에서 발생할 수 있는 비선형성을 최소화하고, 실시간 디지털 로깅·스펙트럼 분석 기능을 제공한다는 점이 향후 광학 메트로노미, 통신, 양자 기술 등 다양한 분야에 적용 가능함을 강조한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기