3D NAND 플래시 메모리 행동 기반 콤팩트 모델 제시

초록

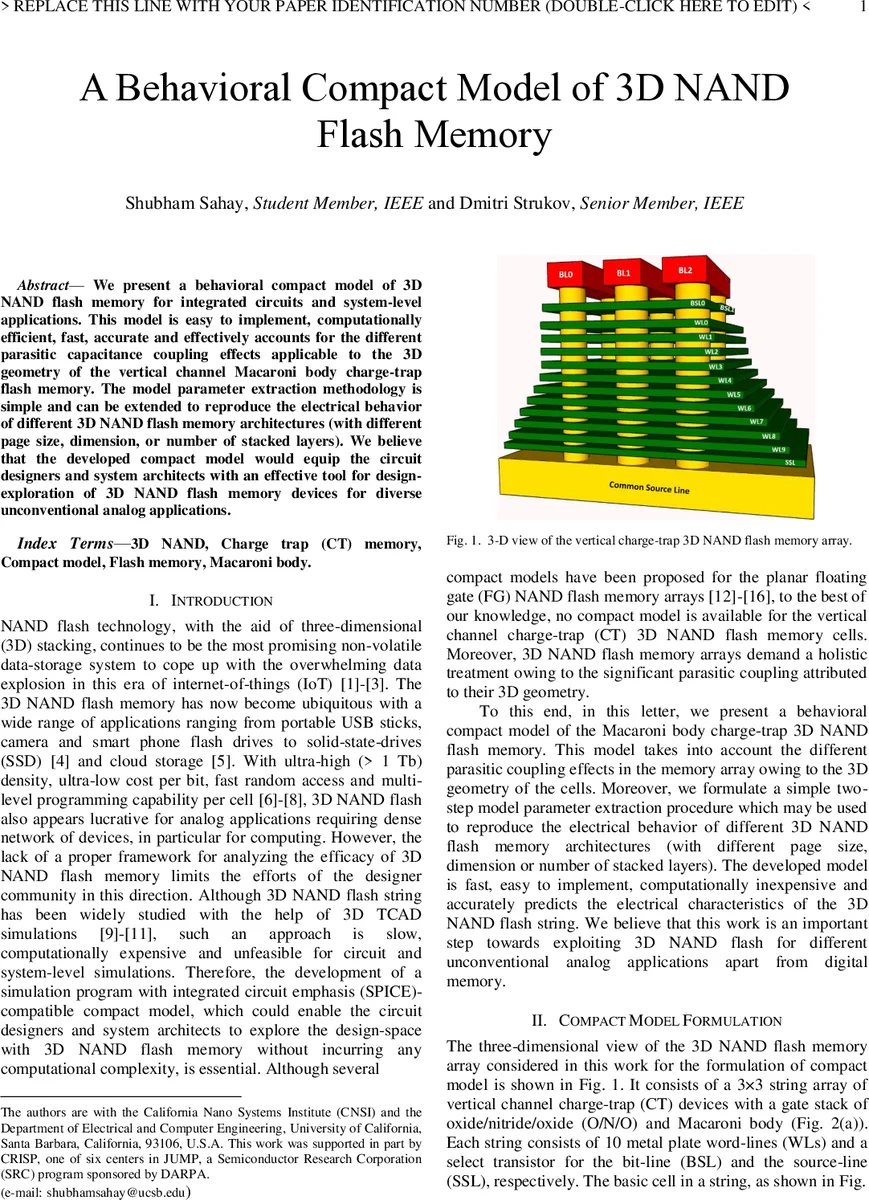

본 논문은 수직 채널 ‘마카로니 바디’ 구조를 갖는 3D NAND 플래시 메모리의 행동 기반 콤팩트 모델을 제안한다. 모델은 수평·수직·대각·측면 커패시턴스 등 3차원 결합 효과를 포함하며, 간단한 2단계 파라미터 추출 절차를 통해 다양한 스택 수와 페이지 크기에 적용 가능하도록 설계되었다.

상세 분석

이 연구는 3D NAND 플래시 메모리 설계 단계에서 회로·시스템 수준 시뮬레이션을 가능하게 하는 행동 기반 콤팩트 모델을 개발하였다. 핵심은 수직 채널 CT(Charge‑Trap) 셀을 폴리실리콘 게이트‑올‑어라운드 나노와이어 FET(GAA‑NWFET) 형태로 모델링하고, 전압 제어 전압원(VCVS)으로 프로그래밍·소거에 따른 임계전압 변화를 재현한다는 점이다. 3×3 배열의 각 셀 사이에 존재하는 수평(C_H), 수직(C_V), 대각(C_D), 측면(C_S) 커패시턴스를 명시적으로 회로 요소로 삽입함으로써 3D 구조 특유의 전기적 결합을 정량화한다. 파라미터 추출은 먼저 TCAD(Sentaurus) 혼합‑모드 시뮬레이션을 이용해 C_V·C_H·C_S 등을 역임피던스 매트릭스로 추출하고, 이후 BSIM‑CMG 110.0.0 모델을 사용해 기본 셀의 트랜스컨덕턴스·용량·채널 저항 등을 맞춘다. 실험 데이터가 부족한 점을 보완하기 위해 동일 구조의 10‑WL 문자열을 TCAD로 재현하고, HSPICE와 연동해 단일 WL 전류‑전압 특성을 검증하였다. 모델은 다중 WL 동시 스위핑 시에도 빠른 수렴성을 보이며, 기존 3D TCAD에 비해 수십 배 빠른 시뮬레이션 시간을 제공한다. 또한, 파라미터 추출 절차가 구조(스택 수, 페이지 크기) 변화에 따라 재사용 가능하도록 설계돼 설계 탐색 단계에서 큰 유연성을 제공한다. 한계점으로는 폴리실리콘 채널의 결정립 경계와 변동성을 무시했으며, 10‑WL 이하의 짧은 문자열만 검증했다는 점이다. 향후 실험 데이터와 더 복잡한 변동 모델을 통합하면 모델 정확도를 더욱 향상시킬 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기