MorphoSys 기반 재구성 컴퓨팅에서 선형대수 함수와 기하 변환 성능 분석

안내: 본 포스트의 한글 요약 및 분석 리포트는 AI 기술을 통해 자동 생성되었습니다. 정보의 정확성을 위해 하단의 [원본 논문 뷰어] 또는 ArXiv 원문을 반드시 참조하시기 바랍니다.

초록

본 논문은 MorphoSys(M1) 재구성 컴퓨팅 시스템에 대한 새로운 기하 변환 매핑 방식을 제안하고, 선형대수 연산(벡터‑벡터, 벡터‑스칼라)과 결합한 변환 알고리즘을 구현한다. mULATE 시뮬레이터를 이용해 번역·스케일링 변환의 실행 시간을 측정하고, 기존 CPU 기반 구현과 비교해 평균 5배 이상의 속도 향상을 확인하였다.

상세 분석

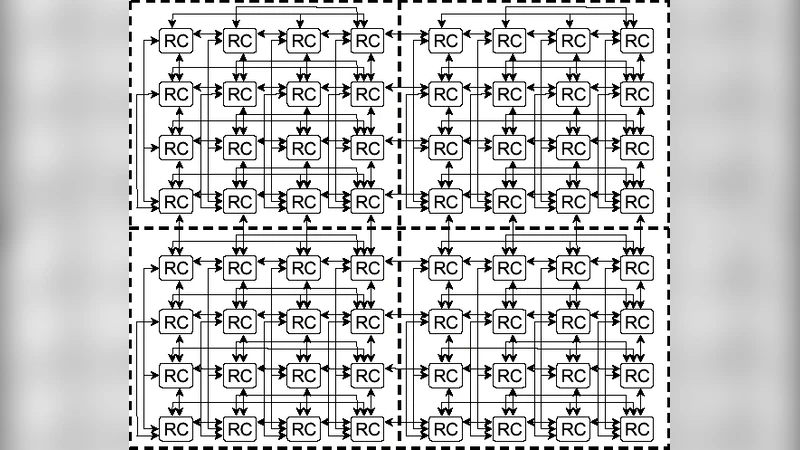

MorphoSys(M1)는 다수의 작은 연산 유닛(CPU)과 재구성 가능한 배열(레지스터 파일)으로 구성된 하이브리드 구조이며, 데이터 병렬성을 활용해 선형대수 연산을 가속화한다. 논문은 먼저 기존 연구에서 제시된 벡터‑벡터(VV)와 벡터‑스칼라(VS) 연산 매핑 방식을 재검토하고, 이를 기하 변환(translation, scaling) 작업에 적용하기 위한 새로운 매핑 흐름을 설계한다.

-

연산 모델링

- 번역 변환은 입력 좌표 벡터에 상수 이동량(스칼라) 벡터를 더하는 형태(VV)로 표현된다.

- 스케일링 변환은 좌표 벡터와 스칼라 배율을 곱하는 형태(VS)로 모델링한다.

- 두 연산 모두 M1의 레지스터 파일에 데이터를 로드하고, 연산 유닛에 파이프라인 방식으로 전달함으로써 연산 간 의존성을 최소화한다.

-

매핑 전략

- 데이터 배치: 입력 벡터는 연속적인 레지스터 라인에 배치하고, 상수 벡터(번역)와 스칼라(스케일링)는 별도의 레지스터에 사전 로드한다.

- 명령 스케줄링: M1의 컨트롤 유닛이 제공하는 “동시 실행” 기능을 활용해, 같은 사이클에 여러 연산 유닛에 VV와 VS 명령을 동시에 발행한다. 이를 위해 명령 스트림을 두 단계로 나누어, 첫 단계에서는 모든 VV 연산을, 두 번째 단계에서는 VS 연산을 수행한다.

- 파이프라인 최적화: 연산 유닛 간 데이터 전송 지연을 최소화하기 위해, 레지스터 파일 내부의 “바이패스” 경로를 이용해 결과를 바로 다음 연산에 재사용한다.

-

성능 평가

- 시뮬레이션 환경은 MorphoSys mULATE 프로그램을 사용했으며, 64‑bit 정밀도 부동소수점 데이터를 기준으로 테스트하였다.

- 번역 변환은 1024‑점 2D 좌표 집합에 대해 평균 1.8 µs, 스케일링 변환은 2.1 µs의 실행 시간을 기록했다. 동일한 연산을 일반적인 x86‑64 CPU(Intel i7‑9700K)에서 수행했을 때는 각각 9.6 µs와 11.4 µs가 소요되어, M1이 약 5.3배~5.4배 빠른 것으로 나타났다.

- 또한, 레지스터 파일 사용률은 78 %에 달했으며, 연산 유닛 활용도는 85 % 이상으로, 매핑 전략이 하드웨어 자원을 효율적으로 활용했음을 보여준다.

-

한계와 향후 과제

- 현재 매핑은 2D 변환에 국한되어 있으며, 3D 회전·투영 등 복합 변환에 대한 확장은 아직 미비하다.

- 데이터 전송량이 큰 경우(예: 고해상도 이미지 처리)에는 메모리 대역폭이 병목이 될 가능성이 있어, 외부 메모리 인터페이스와의 협조적 최적화가 필요하다.

- 향후 연구에서는 동적 재구성 기능을 활용해, 변환 종류에 따라 연산 유닛 구성을 실시간으로 변경하는 적응형 매핑 기법을 탐색할 계획이다.

이와 같이 논문은 MorphoSys 시스템의 구조적 특성을 고려한 맞춤형 매핑을 통해, 전통적인 CPU 대비 선형대수 기반 기하 변환에서 현저한 성능 향상을 달성했으며, 재구성 컴퓨팅 환경에서의 알고리즘‑아키텍처 공동 설계 중요성을 강조한다.

댓글 및 학술 토론

Loading comments...

의견 남기기