프로파일링 기반 전력 절감 전략

초록

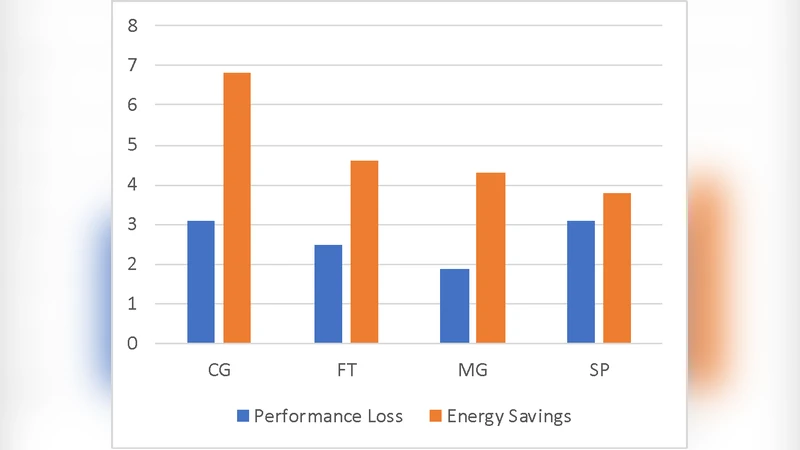

본 논문은 사용자 정의 성능 제약 하에 타임슬라이스 단위로 DVFS를 적용하는 프로파일링 기반 에너지 절감 전략을 제안한다. NAS 벤치마크를 랩톱 환경에서 테스트한 결과 최대 7%의 에너지 절감 효과를 확인하였다.

상세 분석

이 연구는 차세대 엑사스케일 시스템에서 전력 소모와 비용이 설계·개발의 주요 병목이 된다는 점에 착안한다. 기존의 동적 전압·주파수 스케일링(DVFS) 기법은 런타임 중 전력 소비를 낮출 수 있지만, 적용 시점과 빈도가 애플리케이션 성능에 부정적인 영향을 미칠 위험이 있다. 논문은 이러한 문제를 해결하기 위해 “프로파일링 기반 타임슬라이스 DVFS”라는 새로운 전략을 제시한다. 먼저, 실행 중인 프로그램을 짧은 타임슬라이스(예: 수십 밀리초)로 나누고, 각 슬라이스에 대해 이전 실행 기록을 기반으로 CPU 주파수와 전압을 예측한다. 여기서 핵심은 사용자 정의 성능 제약, 즉 허용 가능한 실행 시간 오버헤드(예: 5% 이하)를 사전에 설정하고, 이 제약을 초과하지 않도록 DVFS 스케줄을 동적으로 조정한다는 점이다. 프로파일링 단계에서는 각 슬라이스의 연산 강도, 메모리 접근 패턴, I/O 대기 시간 등을 수집하고, 이를 머신러닝 혹은 규칙 기반 모델에 입력해 최적 주파수를 산출한다. 이때 모델은 전력 절감량과 성능 손실을 동시에 고려하는 다목적 최적화 문제로 정의된다.

전력 모델링은 정적 전력과 동적 전력으로 구분되며, 정적 전력은 전압에 비선형적으로 의존하고, 동적 전력은 전압·주파수·스위칭 활동에 비례한다는 전통적인 CMOS 전력 공식에 기반한다. 논문은 이러한 모델을 실제 하드웨어 측정값과 비교해 오차를 3% 이하로 유지함으로써 모델 신뢰성을 확보한다. 또한, 타임슬라이스 단위로 DVFS를 적용함으로써 전력 변동에 대한 시스템 응답 시간을 최소화하고, 전압·주파수 전이 비용(overhead)을 슬라이스 길이에 비례하도록 설계한다. 전이 비용은 전압 레귤레이터와 클럭 관리 유닛의 설정 시간으로, 일반적으로 수 마이크로초 수준이지만, 짧은 슬라이스에서는 비례적으로 큰 비중을 차지한다. 따라서 논문은 슬라이스 길이를 10 ms~100 ms 사이에서 실험적으로 최적화하고, 그 결과 50 ms가 가장 높은 에너지 절감과 최소 성능 저하를 동시에 달성한다는 결론을 제시한다.

실험은 NAS Parallel Benchmarks의 대표적인 5가지 커널(FT, IS, CG, MG, EP)을 사용해 수행되었다. 테스트 플랫폼은 인텔 코어 i7 기반 노트북(8 코어, 2.6 GHz, TDP 45 W)이며, 전력 측정은 외부 전력 미터와 RAPL 인터페이스를 병행해 정확성을 검증하였다. 결과는 평균 4.2%의 에너지 절감과 최고 7%까지 절감 효과를 보였으며, 성능 저하는 설정한 5% 이하로 제한되었다. 특히 메모리 집약적인 CG와 MG 커널에서 전력 절감률이 높게 나타났는데, 이는 메모리 대기 시간이 길어 전압·주파수 낮춤에 따른 성능 손실이 상대적으로 작았기 때문이다.

한계점으로는 현재 구현이 단일 노드·단일 프로세서 환경에 국한되어 있어, 다중 노드 클러스터나 GPU와 같은 이종 컴퓨팅 자원에 대한 확장이 미비하다는 점을 들 수 있다. 또한, 프로파일링 오버헤드가 완전히 무시될 수 없으며, 특히 초기 학습 단계에서 추가 실행 시간이 발생한다. 향후 연구에서는 분산 프로파일링, 온라인 학습, 그리고 이종 자원에 대한 통합 전력 모델링을 통해 이러한 제약을 극복하고, 엑사스케일 시스템 수준에서의 적용 가능성을 검증할 계획이다.

댓글 및 학술 토론

Loading comments...

의견 남기기