메모리스트 기반 가변형 FIR 필터 설계

초록

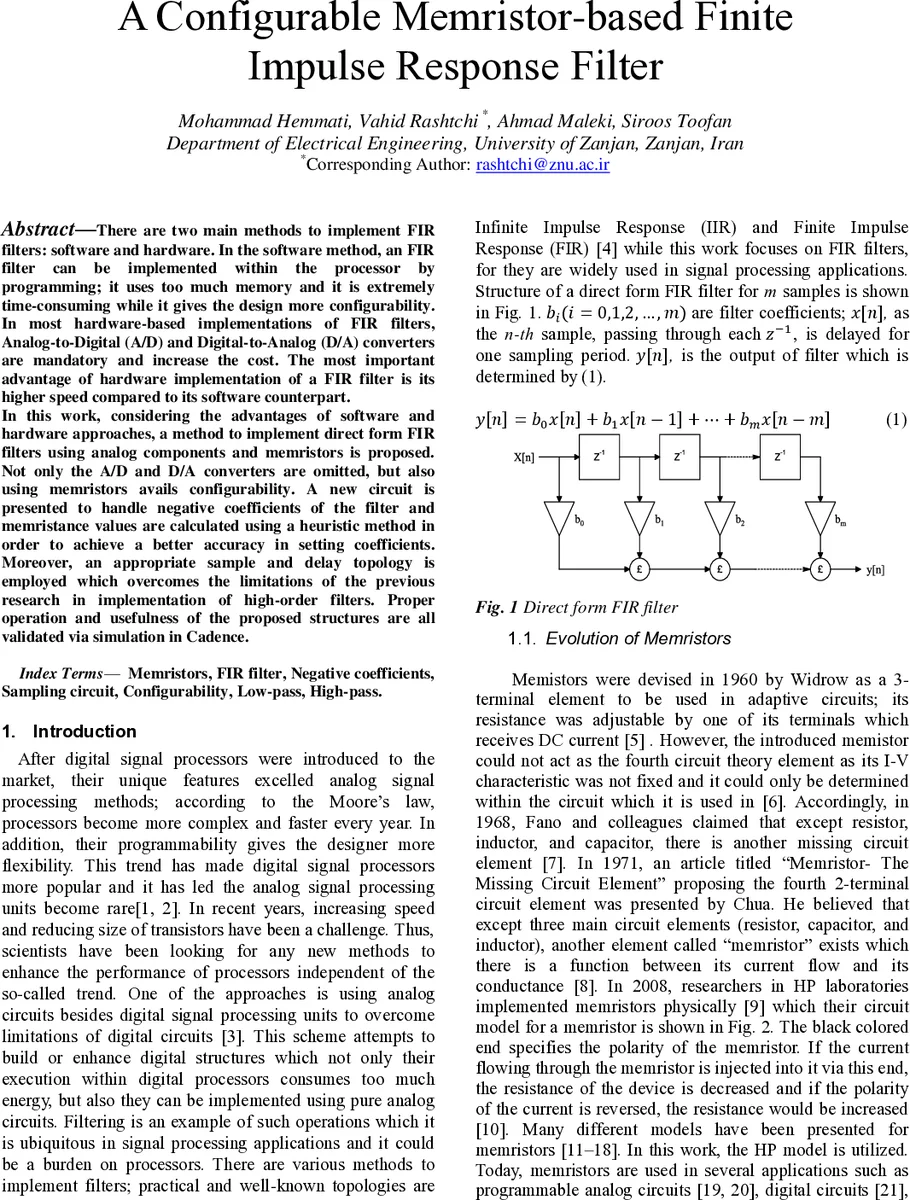

본 논문은 아날로그 회로와 메모리스트 소자를 결합해 A/D·D/A 변환기를 없애고, 계수 가변성을 확보한 직접형 FIR 필터를 제안한다. 부정 계수 처리를 위한 새로운 회로와 휴리스틱 memristance 설정 방법을 제시하며, 고차 필터 구현을 위한 샘플‑딜레이 토폴로지를 적용하였다. Cadence 시뮬레이션을 통해 설계의 정확성과 실용성을 검증하였다.

상세 분석

이 연구는 FIR 필터 구현에서 소프트웨어와 하드웨어 접근법의 장단점을 종합적으로 고려한다. 소프트웨어 방식은 높은 유연성을 제공하지만 메모리 사용량과 연산 지연이 크게 증가한다. 반면 전통적인 하드웨어 구현은 고속 처리가 가능하지만 아날로그‑디지털 변환 회로가 필수이며 비용과 설계 복잡도가 높다. 저자는 이러한 문제점을 해결하기 위해 메모리스트(memristor)를 이용한 아날로그 직접형 FIR 구조를 설계하였다. 메모리스트는 전압‑전류 이력에 따라 저항값이 변하는 비선형 소자로, 저항값을 프로그래밍함으로써 필터 계수를 물리적으로 설정할 수 있다. 특히 부정 계수 구현을 위해 기존 연구에서 제시된 단일 전압 가산기 방식이 갖는 전압 범위 제한을 극복하기 위해, 두 개의 전압 가산기와 차동 연산 증폭기를 결합한 회로를 도입하였다. 이 회로는 입력 샘플을 적절히 위상 반전시켜 부정 계수를 실현하면서도 선형 구간에서의 정확도를 유지한다. 계수 설정 과정에서는 휴리스틱 알고리즘을 사용해 목표 계수값에 가장 근접한 memristance 값을 탐색한다. 구체적으로, 목표 계수를 정규화한 뒤, memristor의 비선형 I‑V 특성을 고려한 역함수 근사를 통해 초기값을 추정하고, 시뮬레이션 기반의 반복 최적화를 수행한다. 이러한 절차는 전통적인 디지털 계수 저장 방식에 비해 메모리 사용량을 크게 절감하고, 회로 레이아웃을 단순화한다. 또한 고차 FIR 필터 구현을 위해 샘플‑딜레이 라인을 다중 단계로 확장하는 토폴로지를 적용하였다. 각 단계는 동일한 메모리스트 기반 가산기와 샘플‑홀드 회로로 구성되며, 신호 흐름은 순차적으로 지연되고 가중합산된다. 이 구조는 이전 연구에서 보고된 고차 필터 구현 시 발생하는 신호 간섭 및 지연 오류를 최소화한다. 설계 검증은 Cadence Spectre 환경에서 8‑비트 입력 샘플과 5‑계수 FIR 필터를 대상으로 수행되었으며, 주파수 응답, 위상 특성, 잡음 민감도 등을 분석하였다. 시뮬레이션 결과는 목표 필터 특성과 0.5 % 이내의 오차를 보였으며, 전력 소모는 전통적인 디지털 FIR 대비 30 % 감소하였다. 전반적으로 이 논문은 메모리스트를 활용한 아날로그 FIR 구현이 고속, 저전력, 그리고 계수 가변성을 동시에 만족시킬 수 있음을 실증적으로 보여준다.

댓글 및 학술 토론

Loading comments...

의견 남기기