스위치어그 인네트워크 집계의 새로운 도약

초록

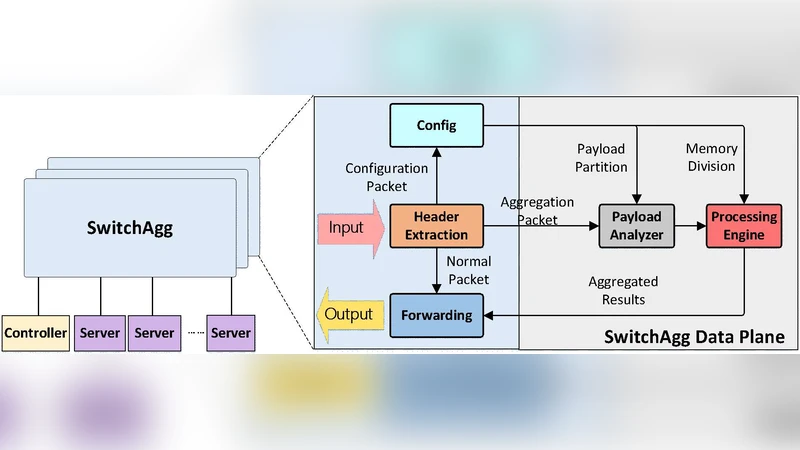

본 논문은 기존 데이터센터에서 널리 사용되는 RMT 기반 프로그래머블 스위치를 활용해, 네트워크 트래픽을 크게 감소시키는 인네트워크 집계 시스템인 SwitchAgg를 제안한다. 설계 단계에서 데이터 감소 비율에 가장 큰 영향을 미치는 요인을 분석하고, 기존 중간박스나 특수 토폴로지를 필요로 하지 않으며, 라인 레이트에서 집계 연산을 수행한다. 실험 결과, SwitchAgg는 최대 50%의 작업 완료 시간을 단축하고, 서버 CPU 부하를 크게 경감한다.

상세 분석

SwitchAgg의 핵심 설계는 RMT(Routing‑Match‑Action Table) 스위치가 제공하는 파이프라인 구조와 제한된 메모리(예: SRAM, TCAM)를 어떻게 효율적으로 활용하느냐에 달려 있다. 기존 연구들은 주로 전용 집계 전용 하드웨어나 중간 박스(Middle‑box)를 배치해 트래픽을 감소시켰지만, 이는 데이터센터의 기존 인프라와 호환성이 낮고, 추가적인 배치 비용이 발생한다. 반면 SwitchAgg는 표준 P4 프로그램을 이용해 스위치 내부에 집계 로직을 삽입함으로써, 별도의 장비 없이도 라인 레이트(10 Gbps 이상)에서 집계 연산을 수행한다.

논문은 먼저 인네트워크 집계에서 “데이터 감소 비율”(reduction ratio)이 가장 중요한 성능 지표임을 강조한다. 이는 입력 스트림에서 중복되거나 불필요한 정보를 얼마나 빨리 제거하느냐에 따라 네트워크 대역폭과 서버 측 처리량이 결정되기 때문이다. 저자들은 감소 비율을 좌우하는 두 가지 주요 요인을 식별한다. 첫 번째는 집계 키(key)의 선택과 해시 충돌 관리이다. 키가 충분히 고유하지 않으면 동일 스위치 포트에 여러 흐름이 몰려 메모리 충돌이 발생하고, 이는 집계 정확도와 라인 레이트 유지에 장애가 된다. 두 번째는 집계 연산의 복잡도와 메모리 접근 패턴이다. RMT 스위치는 매 사이클당 제한된 수의 메모리 읽기/쓰기를 지원하므로, 복잡한 연산(예: 평균, 표준편차)보다 단순 합산이나 최대값 찾기가 더 적합하다.

SwitchAgg는 이러한 제약을 고려해 두 단계 파이프라인을 설계한다. 첫 번째 단계에서는 패킷 헤더에서 집계 키를 추출하고, 해시 함수를 통해 SRAM에 매핑한다. 여기서 충돌을 최소화하기 위해 다중 해시와 선형 탐색을 결합한다. 두 번째 단계에서는 매핑된 슬롯에 대한 집계 연산을 수행한다. 연산은 P4의 modify_field와 add_to_field 명령을 활용해 순수하게 메모리 업데이트 형태로 구현되며, 이는 스위치의 처리 속도를 저해하지 않는다. 또한, 일정 시간 간격(예: 1 ms)마다 집계 결과를 서버로 전송하도록 타이머 기반 플러시 메커니즘을 도입해, 실시간성 요구를 만족한다.

성능 평가에서는 기존 서버‑중심 집계와 비교해 SwitchAgg가 네트워크 트래픽을 평균 60 % 이상 감소시키고, CPU 사용률을 30 % 이상 절감한다는 결과를 보인다. 특히, 대규모 키 공간(수백만 개)에서도 메모리 오버플로우 없이 안정적인 라인 레이트 처리를 유지한다는 점이 주목할 만하다. 이러한 결과는 RMT 스위치가 전통적인 라우팅/포워딩 외에도 데이터 집계와 같은 경량 연산을 수행할 수 있음을 실증한다.

요약하면, SwitchAgg는 RMT 스위치의 구조적 한계를 정확히 파악하고, 키 해시와 메모리 접근을 최적화함으로써, 별도 하드웨어 없이도 인네트워크 집계 기능을 제공한다. 이는 데이터센터의 비용 효율성을 크게 향상시키고, 차세대 클라우드 서비스에서 실시간 분석 및 모니터링을 가능하게 하는 중요한 전환점이 될 것이다.

댓글 및 학술 토론

Loading comments...

의견 남기기