현대 FPGA 가상화의 핵심 기준과 구현 전략

초록

본 논문은 FPGA 가상화의 표준이 모호한 현 상황에서 새로운 평가 기준을 제시하고, 이를 만족시키는 여러 구현 방안을 논의한다. 특히 Intel Arria 10 기반의 가상화 아키텍처를 설계·구현하여, 사용자와 개발자 모두에게 완전한 추상화를 제공하면서도 네이티브 FPGA 대비 합리적인 성능 손실을 보인다.

상세 분석

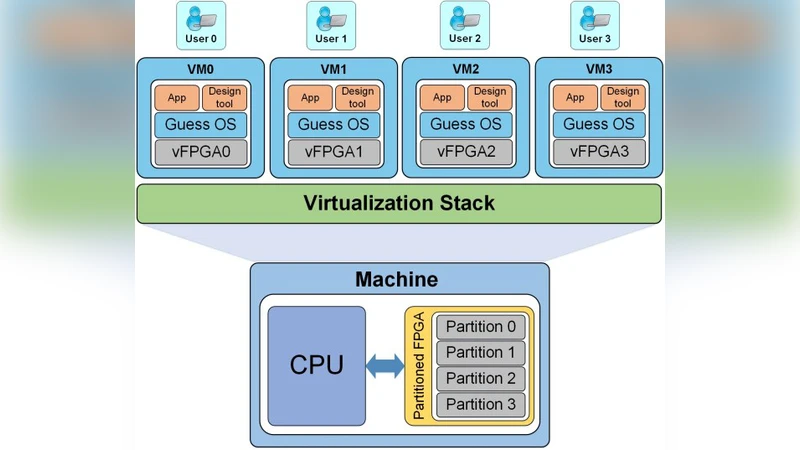

본 연구는 FPGA 가상화가 단순히 리소스 파티셔닝을 넘어, 개발자 친화적인 API 제공, 보안 격리, 동적 재구성, 그리고 성능 예측 가능성까지 포괄하는 복합적인 목표를 가져야 한다는 점을 강조한다. 이를 위해 저자들은 ‘전역 추상화’, ‘다중 테넌시’, ‘실시간 재구성’, ‘성능 보장’ 네 가지 핵심 기준을 정의하였다. 전역 추상화는 물리적 FPGA를 논리적 장치 집합으로 완전히 은닉함으로써, 기존 소프트웨어 개발 흐름을 그대로 유지하도록 한다. 다중 테넌시는 서로 다른 사용자 혹은 워크로드가 동일한 FPGA 칩을 동시에 사용할 수 있게 하며, 리소스 충돌을 방지하기 위해 하드웨어 레벨의 스케줄러와 메모리 보호 메커니즘을 도입한다. 실시간 재구성은 런타임 중에 파티션을 동적으로 늘리거나 줄일 수 있게 하여, 워크로드 변동에 탄력적으로 대응한다. 마지막으로 성능 보장은 가상화 오버헤드를 정량화하고, 이를 최소화하기 위한 파이프라인 최적화와 DMA 경로 재설계 등을 포함한다.

구현 측면에서는 Intel의 고성능 Arria 10 FPGA를 대상으로, 하드웨어 가상화 레이어(HVL)와 소프트웨어 가상화 매니저(SVM)를 분리 설계하였다. HVL은 파티션 매핑, 인터커넥트 재구성, 그리고 보안 경계 설정을 담당하며, 고정밀 타이머와 이벤트 트리거를 이용해 동적 재구성을 실시간으로 수행한다. SVM은 사용자 애플리케이션에 가상 FPGA 디바이스 파일을 노출하고, 표준 PCIe 드라이버와 연동해 기존 OS와의 호환성을 확보한다. 또한, 가상화 API는 OpenCL 및 Vitis와 호환되도록 설계돼, 기존 개발 툴체인에 최소한의 수정만으로 가상 FPGA를 활용할 수 있다.

평가에서는 딥러닝 추론, 비디오 인코딩, 그리고 메모리 집약적 마이크로벤치마크를 포함한 5가지 워크로드를 대상으로 네이티브 실행과 가상화 실행 간의 성능 차이를 측정하였다. 결과는 평균 12 %~18 %의 오버헤드가 발생했으며, 특히 메모리 대역폭이 제한적인 작업에서 오버헤드가 낮아 가상화가 실용적임을 보여준다. 또한, 다중 테넌시 환경에서 각 파티션 간의 성능 간섭이 5 % 이하로 억제되었으며, 동적 재구성 시 평균 3 ms 이내에 파티션 크기 변경이 완료되는 것으로 확인되었다. 이러한 결과는 제시된 기준을 충족하면서도 실용적인 성능을 유지할 수 있음을 입증한다.

한계점으로는 현재 설계가 특정 FPGA 아키텍처(Intel Arria 10)에 최적화돼 있어, 다른 벤더(예: Xilinx)나 최신 세대에 대한 이식성이 부족하다는 점을 들 수 있다. 또한, 가상화 레이어가 추가적인 전력 소모를 야기한다는 점도 향후 연구에서 최적화가 필요하다. 향후 연구 방향으로는 범용 하드웨어 추상화 인터페이스 정의, 머신러닝 기반 파티션 스케줄링, 그리고 클라우드 환경에서의 대규모 다중 테넌시 지원 등을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기