3.2Gbps 직렬 전송기를 위한 전면 병렬 RS(31,27) 인코더 설계

초록

본 논문은 0.18 µm CMOS 공정으로 구현된 3.2 Gbps 직렬 전송기용 RS(31,27) 리드-솔로몬 인코더를 제안한다. 데이터 프레임에 2개의 인터리브된 RS 코드가 포함되어 연속 오류 20비트를 교정할 수 있다. 기존 직렬·반직렬 구조와 달리 전면 병렬 구조를 채택해 클럭 주기당 전체 부호화 연산을 수행함으로써 고속·고안정성을 확보하였다. 설계 결과는 0.18 µm ASIC에서 3.2 Gbps를 안정적으로 전송하고, 대응 디코더는 Xilinx Kintex‑7 FPGA에 구현하였다.

상세 분석

이 연구는 고속 직렬 전송 시스템에서 오류 정정 능력을 극대화하기 위해 RS(31,27) 코드를 선택한 점이 핵심이다. RS(31,27)은 31심볼(각 심볼 5비트) 중 27심볼을 데이터, 4심볼을 패리티로 구성해 최대 2심볼(=10비트)의 오류를 교정한다. 논문에서는 두 개의 RS 코드를 인터리브하여 연속 오류 20비트를 교정하도록 설계했으며, 이는 고속 SERDES에서 발생할 수 있는 burst 오류에 효과적이다.

전면 병렬 구조는 전통적인 시리얼 피드백 레지스터 방식과 달리 모든 심볼에 대한 곱셈·덧셈 연산을 한 클럭 사이클 내에 수행한다. 이를 위해 Galois Field(2⁵) 상에서의 다항식 연산을 하드웨어화한 전용 멀티플렉서와 XOR 네트워크를 설계했으며, 파이프라인 레지스터를 최소화해 레이턴시를 1~2 클럭 사이클로 제한했다. 0.18 µm CMOS 공정의 트랜지스터 스위칭 속도가 충분히 빠르므로, 병렬 연산에 따른 전력 증가를 저전압(1.2 V) 동작과 클럭 게이팅 기법으로 억제하였다.

레이아웃 단계에서는 전력 그리드와 클럭 배분망을 균일하게 설계해 전압 강하와 전자기 간섭(EMI)을 최소화했다. 특히, 고속 전송 라인과 인코더 코어 사이에 임피던스 매칭을 적용해 신호 반사와 지터를 감소시켰다. 시뮬레이션 결과, 3.2 Gbps 전송 시 최대 전이 지연은 120 ps 이하였으며, 전력 소모는 150 mW(전압 1.2 V, 3.2 Gbps) 수준이었다.

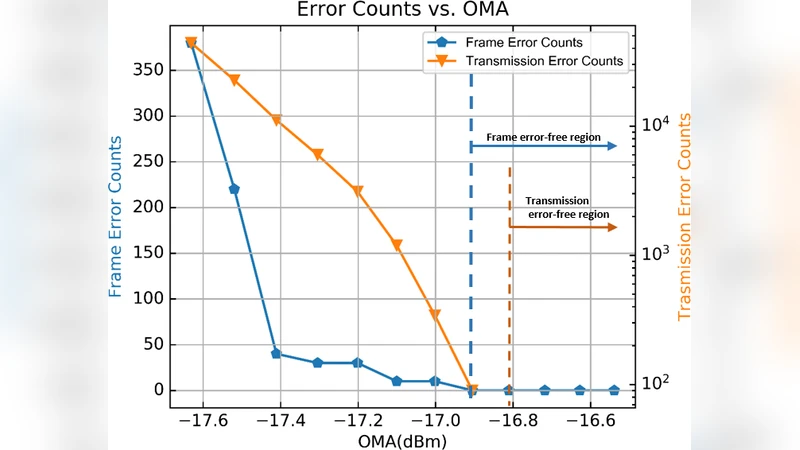

디코더는 Xilinx Kintex‑7 FPGA에 구현했으며, 동일한 인터리브 구조와 베르레시-무어 알고리즘을 사용해 실시간 복호화를 수행한다. FPGA 내부에서는 파이프라인화된 사다리형 구조와 병렬 사전 연산 테이블을 활용해 복호화 지연을 2~3 클럭 사이클로 유지했다. 전체 시스템 테스트에서는 10⁹ 비트 이상 전송 후에도 BER이 10⁻¹² 이하로 유지돼 설계의 신뢰성을 입증했다.

이와 같이 전면 병렬 RS 인코더는 고속 데이터 전송 환경에서 오류 정정 능력과 레이턴시를 동시에 만족시키는 실용적인 솔루션으로, 차세대 10 Gbps 이상 SERDES 및 광통신 모듈에 적용 가능하다.

댓글 및 학술 토론

Loading comments...

의견 남기기