엣지 FPGA용 신경망 가속기 설계 탐색 프레임워크 Systimator

초록

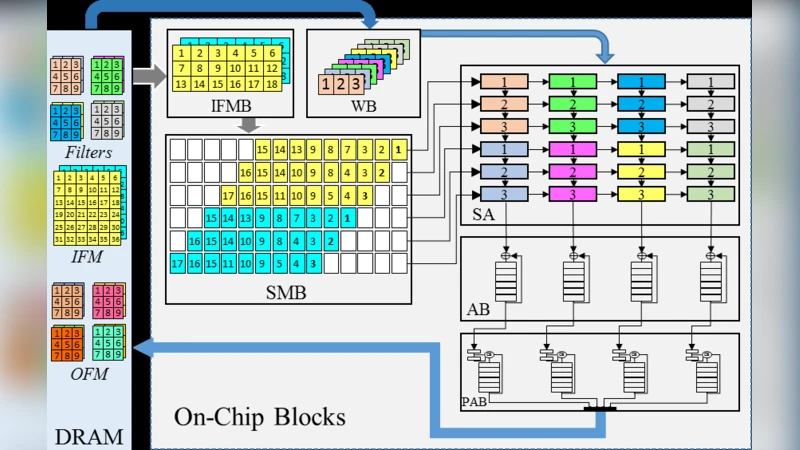

Systimator는 메모리와 DSP 자원이 제한된 저비용 FPGA에서 CNN 가속을 위한 최적의 systolic array 구성을 자동으로 탐색하는 설계 공간 탐색 도구이다. 분석 모델을 통해 타일 크기, 데이터 재사용 방식, 배열 크기 등을 평가하고, 자원 제약을 만족하는 설계 후보들을 성능 순으로 정렬한다. Tiny‑YOLO를 Artix‑7에 매핑한 사례를 제시한다.

상세 분석

본 논문은 엣지 컴퓨팅 환경에서 흔히 사용되는 저비용 FPGA(예: Xilinx Artix‑7)의 제한된 논리, DSP, 블록 RAM 용량을 고려하여, CNN 가속에 적합한 systolic array 구성을 선택하는 문제를 체계적으로 해결한다. 핵심은 두 단계의 설계 공간 탐색이다. 첫 단계에서는 입력 피처맵(IFM)과 가중치의 타일링 파라미터, systolic array의 행·열 수, 동시에 처리할 채널 수 등을 조합해 가능한 설계점들을 생성하고, 각 설계점에 대해 IFM 버퍼, 가중치 버퍼, 스크래치패드, 누적 블록, 풀링·활성화 블록 등에 요구되는 온칩 메모리를 분석식(식 3‑6)으로 정량화한다. 메모리 요구량이 FPGA의 BRAM 한도를 초과하면 해당 설계점은 폐기한다. 두 번째 단계에서는 남은 설계점에 대해 데이터 전송·연산·출력 저장에 소요되는 사이클을 식 11‑16을 이용해 추정하고, 평균 메모리 대역폭과 비중첩 타일 전송을 가정해 전체 처리 시간을 계산한다. 데이터 재사용 전략을 ‘피처맵 재사용’과 ‘필터 재사용’ 두 가지로 구분함으로써, 동일한 하드웨어 자원에서도 서로 다른 메모리·연산 균형을 탐색한다. 설계점 수는 타일 크기 후보(F), 행·열 후보(P, Q, R) 등에 따라 조합적으로 증가하지만, 제시된 식들은 복잡한 시뮬레이션 없이 빠른 평가를 가능하게 한다. 실험에서는 Tiny‑YOLO의 96개 설계점을 조사했으며, 자원 제한을 만족하면서도 최고 성능을 보이는 배열 크기와 타일링 조합을 도출했다. 또한, 설계 탐색 스크립트를 오픈소스로 제공해 재현성과 확장성을 확보하였다. 이 접근법은 기존 연구가 고성능 FPGA에 초점을 맞추어 로컬 인터커넥트를 충분히 활용하지 못하거나, 단일 데이터 재사용 패턴만 고려했던 한계를 극복한다.

댓글 및 학술 토론

Loading comments...

의견 남기기