FPGA 기반 고속 양자키분배용 가우시안 난수 발생기

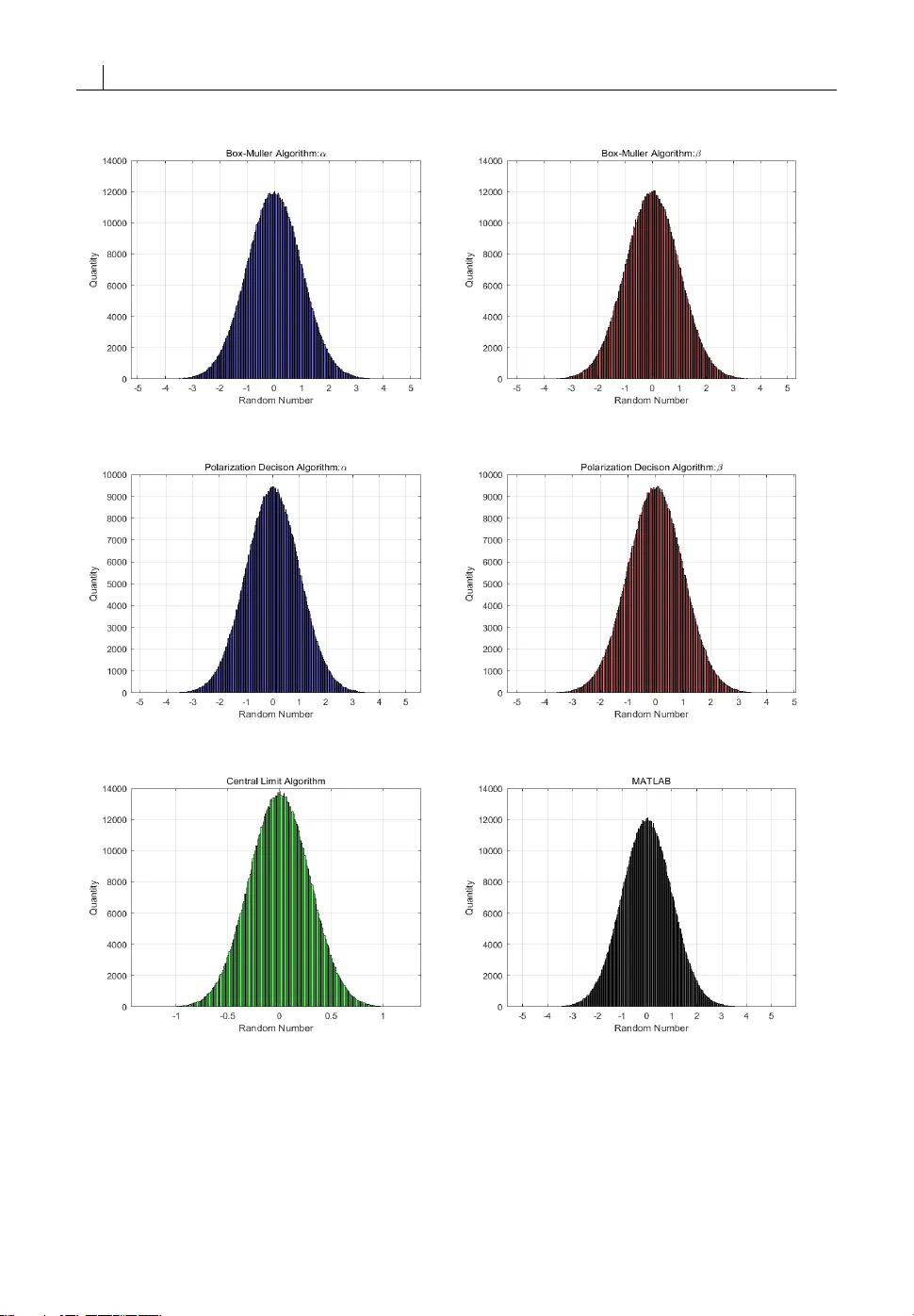

** 본 논문은 양자키분배(QKD) 시스템에 필요한 고품질·고속 가우시안 난수 생성기를 FPGA로 구현한다. Uniform RNG는 32‑bit 다중 반환 시프트 레지스터(MSRG)로 구현하고, 세 가지 알고리즘(Box‑Muller, Polar(Polarization Decision), Central‑Limit)을 비교한다. 자원 소모와 통계적 품질(귀무가설 검정) 측면에서 Polar 알고리즘이 가장 효율적이며, 중앙극한법은 꼬리 부분에서 …

저자: Yue Hu, Yan Wu, Yi Chen

**

양자키분배(QKD)는 양자역학의 불확정성 원리를 이용해 두 통신 당사자 사이에 절대적인 비밀키를 공유하는 기술이다. 특히 연속 변수(CV) QKD에서는 키의 변조에 가우시안 난수가 필수적이며, 난수의 품질과 생성 속도가 시스템 보안 및 전송 효율을 좌우한다. 본 논문은 이러한 요구를 충족시키기 위해 FPGA(Field‑Programmable Gate Array) 기반의 고속 가우시안 난수 발생기(GRNG)를 설계·구현하고, 세 가지 전통적인 알고리즘인 Box‑Muller, Polarization Decision(Polar) 및 Central‑Limit을 비교 분석한다.

**1. 시스템 구조와 균등 난수 생성**

모든 알고리즘은 기본적으로 (0,1) 구간의 균등 난수(URN)가 필요하다. 이를 위해 저자들은 다중 반환 시프트 레지스터(MSRG) 기반의 LFSR를 선택했으며, 특성 다항식 f(x)=x³²+x⁸+x⁵+x²+1을 사용해 2³²‑1의 최대 주기를 확보하였다. 생성된 32‑bit 시퀀스를 정수형으로 나누어 실수형 URN으로 변환한다. MSRG는 하드웨어 구현이 간단하고, LUT와 FF만으로 구현 가능해 FPGA 자원 소모를 최소화한다.

**2. 알고리즘 별 구현 방식**

- **Box‑Muller**: 두 개의 URN(U₁, U₂)을 로그와 삼각함수 변환을 통해 α=√(-2lnU₁)·sin(2πU₂), β=√(-2lnU₁)·cos(2πU₂) 로 계산한다. FPGA에서는 LOG, SQRT, SIN, COS 모듈과 4개의 멀티플라이어가 필요하며, 연산 파이프라인이 복잡해 DSP와 LUT 사용량이 크게 증가한다.

- **Polar (Polarization Decision)**: U₁, U₂를 이용해 s=U₁²+U₂²가 1보다 작을 때만 계산을 진행한다. 조건을 만족하면 α=U₁·√(-2ln s)/s, β=U₂·√(-2ln s)/s 로 변환한다. 이 방식은 거부 샘플링을 사용해 불필요한 연산을 줄이며, LOG, SQRT, DIV, MULT 모듈만으로 구현 가능해 자원 효율성이 높다.

- **Central‑Limit**: n개의 URN을 합산(S=∑Uᵢ)하고, 평균을 정규화해 Z=(S‑n/2)/√(n/12) 로 가우시안 근사를 만든다. 하드웨어는 단순히 n개의 덧셈 회로와 하나의 나눗셈 회로만 필요해 가장 가볍지만, n이 충분히 크지 않으면 꼬리 부분에서 편차가 발생한다.

**3. 하드웨어 아키텍처**

각 알고리즘은 싱글‑프리시전 부동소수점(FP32) 연산을 기반으로 설계되었다. Box‑Muller와 Polar는 각각 4~5개의 외부 멀티플라이어와 LOG, SQRT, DIV 모듈을 사용한다. 중앙극한법은 덧셈 회로와 하나의 DIV만 필요해 가장 적은 DSP를 차지한다. 전체 설계는 Vivado를 이용해 Xilinx Kintex‑7 FPGA에 매핑했으며, 자원 사용량은 다음과 같다(예시):

- Box‑Muller: LUT 12 % / FF 10 % / DSP 8 %

- Polar: LUT 8 % / FF 7 % / DSP 5 %

- Central‑Limit: LUT 4 % / FF 3 % / DSP 2 %

**4. 성능 및 통계 검증**

생성된 난수는 1 × 10⁶ 샘플을 추출해 Kolmogorov‑Smirnov, χ², Anderson‑Darling, Shapiro‑Wilk, 그리고 Q‑Q 플롯을 포함한 5가지 검정을 수행했다. 세 알고리즘 모두 95 % 신뢰수준 이하의 p‑값을 보여 정규성 가설을 기각하지 못했으며, 특히 Polar 알고리즘은 가장 높은 p‑값을 기록해 통계적 품질이 우수함을 입증했다. 중앙극한법은 꼬리 영역에서 p‑값이 다소 낮아 실제 QKD에서 요구하는 높은 엔트로피를 완전히 만족시키지 못할 가능성이 있다.

**5. 처리 속도와 실용성**

FPGA 구현은 200 MS/s 이상의 연속 출력 속도를 달성했으며, 이는 동일한 알고리즘을 CPU에서 소프트웨어로 실행할 때보다 10배 이상 빠른 수치이다. 낮은 전력 소모와 높은 병렬 처리 능력 덕분에 실시간 CV‑QKD 시스템에 바로 적용 가능하다. 또한, 2³²‑1의 긴 주기는 장기간 운용 시 주기 반복에 따른 보안 약화를 방지한다.

**6. 결론 및 향후 과제**

본 연구는 FPGA 기반 GRNG 설계가 QKD 시스템에 필수적인 고속·고품질 난수 공급을 실현함을 증명한다. 특히 Polar 알고리즘이 자원 효율성과 통계적 정확도 측면에서 최적임을 확인했으며, 중앙극한법은 간단하지만 보안 민감도가 높은 응용에는 부적합할 수 있다. 향후 연구에서는 더 높은 비트 정밀도(예: 64‑bit 부동소수점)와 다중 채널 병렬화를 통해 키 전송률을 더욱 확대하고, 양자 난수 인증 프로토콜과의 연동을 검증할 계획이다.

**

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기