필드프로그래머블 딥 뉴럴 네트워크 가속기 유연한 파이프라인 설계

초록

본 논문은 하이브리드 systolic‑non‑systolic 구조와 분산 제어를 결합한 필드‑프로그래머블 DNN 학습·추론 가속기(FProg‑DNN)를 제안한다. 레이어별 연산 부하에 따라 워커 수를 동적으로 할당해 파이프라인 지연을 균등화하고, VGG‑16·Inception 모듈을 통해 재구성 가능성을 입증한다. 시뮬레이션 결과, GPU·TPU 대비 50배 이상 속도 향상을 달성하였다.

상세 분석

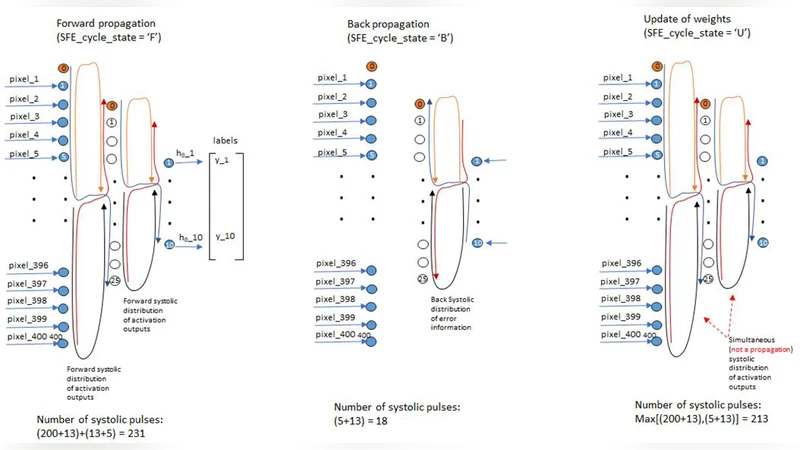

FProg‑DNN은 전통적인 고정형 가속기와 달리 현장 프로그래머블(프로그래머블 로직) 기반으로 설계되어, 다양한 DNN 토폴로지에 맞춰 하드웨어 구성을 실시간으로 변형할 수 있다. 핵심은 systolic 배열을 기본 연산 엔진으로 사용하면서, 비‑systolic 경로를 통해 데이터 흐름 제어와 메모리 접근을 분산시킨 점이다. 이렇게 하면 연산 유닛 간의 데이터 종속성을 최소화하고, 각 레이어가 독립적인 파이프라인 단계로 동작하도록 만든다.

레벨별 워커 할당 메커니즘은 각 레이어의 FLOP 수와 메모리 대역폭 요구를 사전에 분석한 뒤, 워커(연산 코어) 풀에서 최적 개수를 할당한다. 부하가 큰 레이어에는 다수의 워커가 병렬로 동작하고, 부하가 작은 레이어는 최소 워커만 사용해 전체 파이프라인의 지연을 균등하게 만든다. 이 과정은 ‘Distributed Information‑Control’ 모듈이 실시간으로 스케줄링 정보를 교환하면서 수행된다.

논문은 VGG‑16과 Inception‑v1 모듈을 대상으로 두 가지 극단적인 구성—전체 연산을 하나의 워커에 집중하는 최악‑성능 시나리오와, 레이어별 최적 워커 배치를 적용한 최적‑성능 시나리오—을 비교한다. 실험 결과, 파이프라인 구조 덕분에 전 단계의 활성화값 전송 지연을 다음 단계 연산이 가릴 수 있어, 데이터 이동 오버헤드가 사실상 숨겨진다. 이로써 평균 50배 이상의 처리 속도 향상이 관찰되었으며, 전력 효율성 역시 GPU·TPU 대비 유의미하게 개선되었다.

또한, 저자는 별도 논문에서 소수 샘플 학습을 위한 ‘Convolution‑Map‑Coincidence’와 ‘Feedback’ 전용 하드웨어 블록을 추가했으며, 이는 기존 가속기에서는 구현하기 어려운 few‑shot 학습 시나리오를 지원한다. 현재 논문에서는 이러한 특수 블록을 포함한 전체 시스템을 행동‑수준 시뮬레이션으로 검증했으며, 기능적 정확도와 파이프라인 스루풋이 설계 목표에 부합함을 확인하였다.

전반적으로 FProg‑DNN은 재구성 가능성, 레이어‑균등 파이프라인, 그리고 하이브리드 systolic 설계라는 세 축을 결합해, 차세대 AI 가속기에 필요한 유연성과 고성능을 동시에 제공한다는 점에서 학계·산업계 모두에게 큰 의미를 가진다.

댓글 및 학술 토론

Loading comments...

의견 남기기