고속 저전력 CIC 필터 VLSI 구현 및 최적화

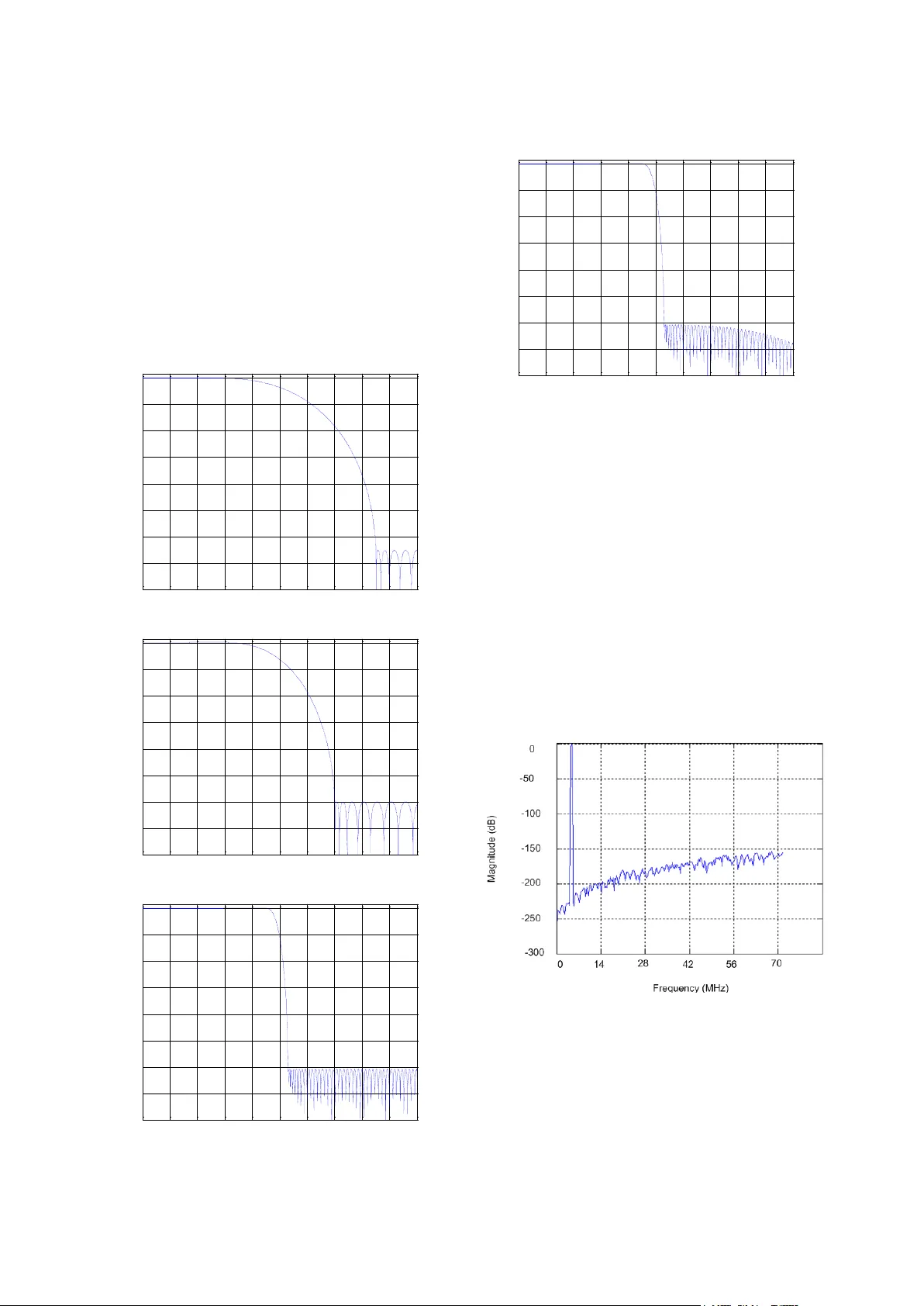

본 논문은 σ‑Δ 변조기의 디시메이션에 널리 사용되는 Cascaded Integrator‑Comb(CIC) 필터를 고속·저전력 VLSI 구조로 구현한다. 파이프라인 적분기와 수정형 캐리‑룩어헤드 가산기(MCLA)를 도입해 연산 지연을 최소화하고, 단계별 트렁케이션으로 레지스터 폭을 축소해 면적·전력을 절감한다. MATLAB‑Simulink와 Verilog HDL 시뮬레이션을 통해 주파수 응답과 SNR을 검증했으며, FPGA 구현에서 22 MHz…

저자: Rozita Teymourzadeh, Masuri Othman

본 논문은 고속·저전력 디지털 신호 처리에 필수적인 Cascaded Integrator‑Comb(CIC) 필터의 VLSI 구현 방안을 제시한다. 서론에서는 σ‑Δ 변조기의 과샘플링 특성으로 인해 디시메이션이 필수적이며, CIC 필터가 곱셈 없이 구현 가능한 경제적인 구조임을 강조한다. Hogenauer가 제안한 기본 CIC 구조를 바탕으로, 필터는 N단의 적분기와 N단의 컴브, 그리고 R배 다운샘플러로 구성된다. 전송함수 H(z) =

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기