디지털 슬라이싱 기반 고속 FFT 버터플라이 설계 및 FPGA 구현

초록

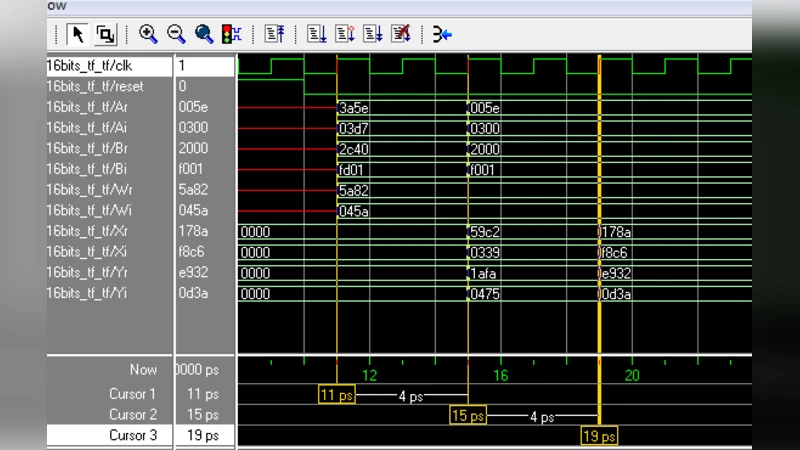

본 논문은 FFT 연산의 핵심인 버터플라이 구조에 디지털 슬라이싱 기법을 적용하여 곱셈 연산을 상수 곱 전용 구조로 대체한다. 16‑bit 고정소수점 입력을 4‑bit 블록 4개로 분할하고, 미리 저장된 트위들 팩터와의 곱셈을 슬라이스별 가산·시프트 연산으로 구현한다. Xilinx Virtex‑II FPGA에 Verilog로 구현한 결과, 기존 멀티플라이어 기반 버터플라이에 비해 최대 클럭 주파수가 535.9 MHz(슬라이스 버터플라이) vs 198.98 MHz(기존)로 2.7배 향상되었으며, 논리 게이트 수는 약 31 k게이트(슬라이스) vs 18 k게이트(기존)로 증가한다.

상세 분석

이 논문은 FFT 구현에서 가장 큰 지연을 초래하는 복소수 곱셈을 최소화하기 위해 ‘디지털 슬라이싱(Digit‑Slicing)’ 기법을 적용한 새로운 버터플라이 구조를 제안한다. 입력 신호를 16‑bit 2’s‑complement 고정소수점으로 가정하고, 이를 4‑bit 길이의 4개 블록으로 나누어 각각을 독립적인 가산·시프트 연산으로 변환한다. 트위들 팩터는 사전에 ROM에 저장된 상수이며, 슬라이스별 곱셈은 상수와의 곱셈이므로 곱셈기 자체를 구현하지 않고도 결과를 얻을 수 있다. 이 방식은 전통적인 복소수 곱셈이 요구하는 4개의 실수 곱셈과 2개의 실수 가산을 대체한다.

구조적 관점에서 보면, 슬라이스된 데이터는 가중치(2^(p·k))에 따라 재조합되며, 각 블록은 동일한 연산 흐름을 갖는다. 따라서 파이프라인화가 용이하고, FPGA의 LUT와 DSP 블록을 최소한으로 사용하면서 높은 클럭 주파수를 달성한다. 구현 결과는 두 가지 모듈을 비교했을 때, 슬라이스 버터플라이가 535.9 MHz의 최대 주파수를 기록했으며, 이는 기존 멀티플라이어 기반 버터플라이(198.98 MHz)보다 2.7배 빠른 속도이다. 다만 논리 게이트 수가 31 k게이트로 18 k게이트보다 약 73 % 증가하므로 면적·전력 효율성 측면에서 트레이드오프가 존재한다.

또한, 논문은 기존의 디지털 필터에 적용된 슬라이스 기법을 FFT에 확장한 점을 강조한다. 이전 연구

댓글 및 학술 토론

Loading comments...

의견 남기기