고속 푸리에 변환을 위한 파이프라인 디지털 슬라이싱 무곱셈 버터플라이 온칩 구현

초록

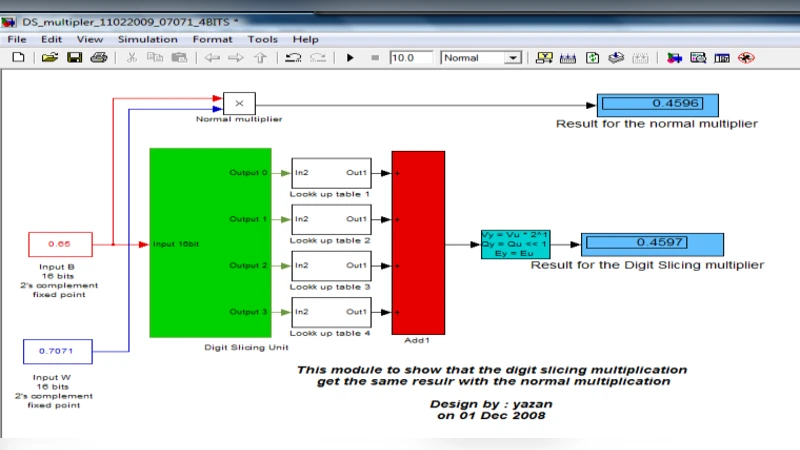

본 논문은 Radix‑2 DIT FFT에서 가장 연산량이 큰 복소수 곱셈을 디지털 슬라이싱 기반의 상수 전용 곱셈기(ROM‑LUT)로 대체하고, 파이프라인 구조를 적용해 FPGA 상에서 549.75 MHz의 최고 클럭을 달성한 설계를 제시한다. 기존 멀티플라이어 기반 버터플라이 대비 약 2.8배 빠른 속도와 적은 게이트 수를 보인다.

상세 분석

FFT는 디지털 신호 처리에서 핵심 알고리즘이며, 특히 Radix‑2 DIT 구조는 구현이 간단하지만 복소수 곱셈이 병목이 된다. 논문은 이 병목을 해소하기 위해 두 가지 핵심 기술을 결합한다. 첫째, ‘디지털 슬라이싱(digit‑slicing)’ 기법을 이용해 입력 데이터를 4비트 블록으로 나누고, 각 블록에 대해 미리 계산된 곱셈 결과를 16‑entry ROM에 저장한다. 이렇게 하면 실제 곱셈 회로 없이도 상수(트윌리 팩터)와의 곱을 LUT‑lookup + 간단한 가산기로 구현할 수 있다. 둘째, 이러한 슬라이스‑곱셈 유닛을 파이프라인 단계에 배치해 연산 지연을 최소화하고, 복소수 덧셈·뺄셈은 Kogge‑Stone 및 Stone‑Ling 가산기를 사용해 고속화한다. 설계는 Verilog로 기술되어 Xilinx Virtex‑II XC2V500‑6FG456에 합성되었으며, 전체 게이트 수는 31 159게이트, 최대 동작 주파수는 549.75 MHz(버터플라이)와 609.98 MHz(단일 상수 곱셈‑리스)로 측정되었다. 기존 멀티플라이어 기반 버터플라이가 198.987 MHz, 일반 멀티플라이어가 220.160 MHz에 머물렀던 것과 비교해 각각 276 %·277 % 향상된 것이다. 이 결과는 상수 곱셈이 미리 알려진 FFT 트윌리 팩터에 특화된 경우, 곱셈 회로를 완전히 제거함으로써 면적·전력·속도 모두에서 이점을 얻을 수 있음을 실증한다. 또한, 파이프라인 구조와 ROM‑LUT 설계가 FPGA 내부 자원을 효율적으로 활용함을 보여준다. 다만, 설계는 4‑bit 슬라이스와 고정된 상수에 의존하므로, 가변‑정밀도나 비정수‑계수 FFT에는 추가적인 변환 로직이 필요할 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기