게이트형 임계값 로직을 이용한 근사 확률 신경망 하드웨어 구현

초록

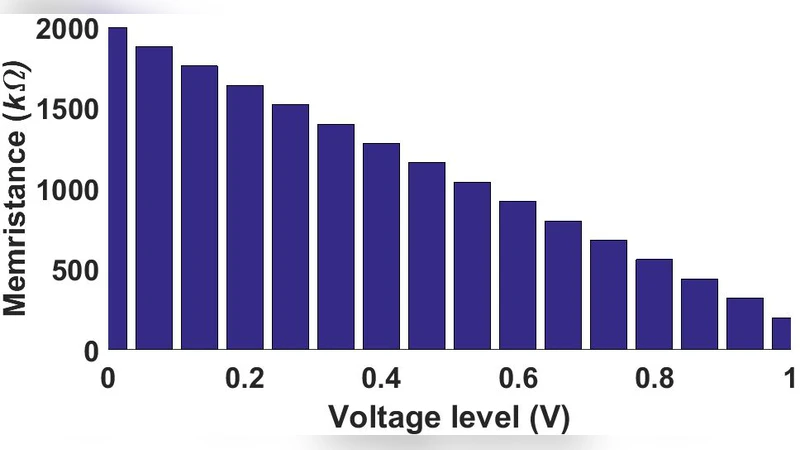

본 논문은 확률 신경망(PNN)의 지수 연산을 게이트형 임계값 로직으로 대체하고, 가중치를 16단계로 양자화한 메모리스트 교차배열(Memristive Crossbar) 기반 근사 PNN(APNN) 회로를 제안한다. 정규화·양자화 과정을 통해 회로 복잡도를 크게 낮추면서, 적응형 임계값 방식을 적용해 분류 정확도를 98 % 이상 달성하였다. SPICE와 MATLAB 시뮬레이션을 통해 전력 124 mW, 면적 5.8 mm²의 소형 아날로그 구현 가능성을 입증한다.

상세 분석

이 연구는 기존 PNN이 갖는 지수 함수 구현의 비선형성 및 대규모 가중치 저장 문제를 두 가지 핵심 아이디어로 해결한다. 첫째, 지수 연산 (e^{-(xW)^2/2\sigma^2}) 을 “(|xW-\sigma|<\theta)”와 같은 임계값 비교로 근사함으로써 아날로그 회로에서 복잡한 연산을 단순히 비교 연산으로 치환한다. 이때 임계값 (\theta) 는 학습 단계에서 각 클래스별로 최적화되는 적응형 임계값 로직을 사용한다. 둘째, 가중치를 GST‑멤리스터 기반 교차배열에 저장하고 16단계(4‑bit) 양자화함으로써 메모리 요구량과 회로 면적을 크게 감소시킨다. 교차배열은 입력 전압을 행에, 학습 샘플을 열에 매핑해 전류‑전압 변환(I‑V) 연산을 수행하고, 전류 버퍼와 현재‑전압 변환기(IVC)로 신호를 정규화한다. 비교기와 승자‑점유(WTA) 회로를 통해 각 클래스의 평균 출력값을 계산하고 최종 클래스를 결정한다. 회로 설계는 180 nm CMOS 공정 기반이며, 트랜지스터 크기와 커패시터 값이 상세히 제시돼 재현성을 높인다. 시뮬레이션 결과, 고정 임계값 방식에서는 양자화된 가중치가 정확도 58 %로 급락하지만, 적응형 임계값을 적용하면 98.9 %까지 회복한다. 전력 분석에서는 OpAmp가 가장 큰 소비원이며, 저전압 OpAmp 교체로 개선 가능성을 제시한다. 논문은 또한 멤리스터 비선형성, 공정 변동, 대규모 확장성 등 아직 해결해야 할 과제를 명시한다. 전체적으로, 비선형 연산을 논리 비교로 대체하고, 멤리스터 교차배열을 활용한 근사 PNN은 아날로그 하드웨어 구현에서 속도·전력·면적 효율을 크게 향상시킬 수 있음을 보여준다.

댓글 및 학술 토론

Loading comments...

의견 남기기