고속 파이프라인 CIC 필터의 VLSI 구현과 무선 수신기 적용

초록

본 논문은 5‑bit Σ‑Δ ADC 출력에 맞춘 5단계 고속 CIC 디시메이션 필터를 설계하고, 파이프라인 구조와 캐리 룩어헤드 가산기(CLA)를 적용해 FPGA와 ASIC에서 332 MHz 이상의 클럭 주파수를 달성한 결과를 제시한다. 전력 3.1 mW, 면적 0.308 mm²(0.18 µm) 수준으로 무선 통신 수신기에 적합한 고성능·저전력 솔루션을 제공한다.

상세 분석

이 연구는 Σ‑Δ 변조기에서 발생한 고속 5‑bit 데이터 스트림을 효율적으로 디시메이션하기 위해 기존 Hogenauer CIC 구조를 개선한 새로운 알고리즘을 제안한다. 필터 차수 N=5, 차분 지연 M=1, 디시메이션 비 R=16을 선택함으로써 레지스터 폭 증가를 최소화하고 오버플로우를 방지한다. 핵심 개선점은 세 가지이다. 첫째, 각 단계에서 불필요한 LSB를 제거하는 트렁케이션 기법을 적용해 내부 워드 길이를 25→22→20→18→16 bit로 단계적으로 감소시켜 레지스터 면적과 전력 소모를 크게 낮추었다. 둘째, 전통적인 파이프라인 레지스터를 적층하지 않고도 적분기 단계에만 파이프라인을 삽입함으로써 클럭 주기 제한 요소인 최상위 비트 전파 지연을 최소화하였다. 이는 전체 파이프라인 구조가 단순하면서도 높은 처리량을 유지하게 한다. 셋째, 8‑bit 캐리 룩어헤드 가산기(CLA)를 5단계에 걸쳐 배치해 연산 속도를 크게 향상시켰다. CLA는 4‑bit 블록 단위로 generate·propagate 신호를 생성하고, 이를 계층적으로 결합해 캐리 전파 시간을 O(log n)으로 감소시킨다. 설계에서는 25‑bit까지 확장 가능한 구조를 유지하면서도 각 단계별 비트 폭에 맞춰 4‑bit CLA 모듈을 조합하였다.

Verilog HDL 코드는 Xilinx ISE 환경에서 시뮬레이션 및 합성을 수행했으며, Virtex‑II FPGA 보드에 구현해 실제 동작을 검증하였다. 합성 결과 최소 클럭 주기 1.9 ns(최대 주파수 503 MHz)로, 설계 목표인 332 MHz를 충분히 초과하였다. ASIC 구현은 0.18 µm Silterra와 0.35 µm Mimos 공정으로 수행했으며, 활성 코어 면적은 0.308 mm × 0.308 mm, 전력 소모는 3.1 mW(0.18 µm)와 6.03 mW(0.35 µm)로 보고되었다.

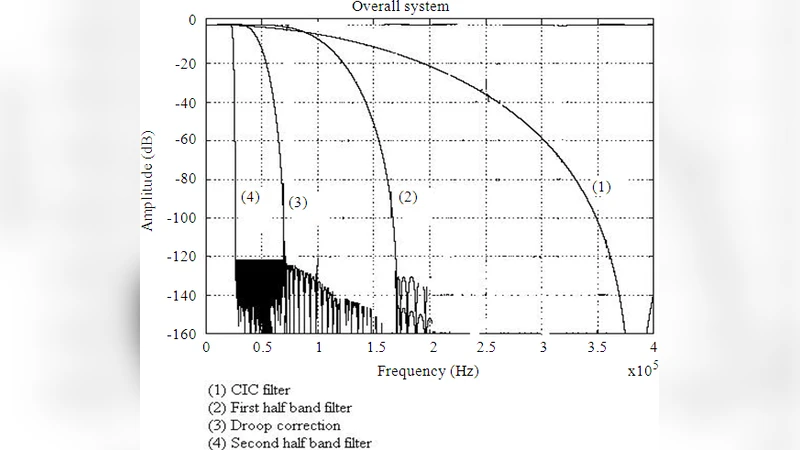

성능 측면에서 전체 디시메이션 체인(첫 번째 CIC 필터 + 두 개의 하프밴드 필터 + 드롭 보정 필터)의 주파수 응답은 7 kHz~384 kHz 대역을 통과시키며, 98 dB의 동적 범위와 145 dB에 달하는 SNR 향상을 달성한다. 이는 무선 통신, 특히 4G 및 차세대 시스템에서 요구되는 고해상도·고속 ADC 전처리 단계에 충분히 부합한다.

본 논문의 주요 기여는 (1) 트렁케이션과 파이프라인을 결합한 고속·저전력 CIC 구조, (2) 맞춤형 8‑bit CLA 가산기를 이용한 연산 가속, (3) FPGA와 ASIC 양쪽에서 실증된 설계 흐름 및 상세 합성/배치 결과 제공이다. 다만, 설계가 5‑bit 입력에 최적화돼 있어 더 높은 비트 폭(예: 12‑bit 이상) Σ‑Δ 변조기와의 직접 연계에는 추가적인 워드 길이 관리와 오버플로우 방지 설계가 필요할 것으로 보인다. 또한, 트렁케이션에 따른 양자화 잡음이 무선 수신기의 최악 상황에서 어떻게 누적되는지에 대한 정량적 분석이 부족한 점은 향후 연구 과제로 남는다.

댓글 및 학술 토론

Loading comments...

의견 남기기