IPBus 기반 I2C 관리 시스템 설계 및 구현

초록

본 논문은 CBM DAQ 시스템에서 사용되는 AFCK 보드와 FMC 모듈의 I2C 장치를 IPBus를 통해 제어하기 위한 초기화 및 운영 모듈을 설계하고 검증한 내용을 다룬다. 전원 공급 시 ROM에 저장된 명령으로 필수 I2C 장치를 자동 초기화하고, 이후 Wishbone 인터페이스를 갖는 I2C 마스터를 IPBus 슬레이브로 연결해 실시간 제어가 가능하도록 구현하였다.

상세 분석

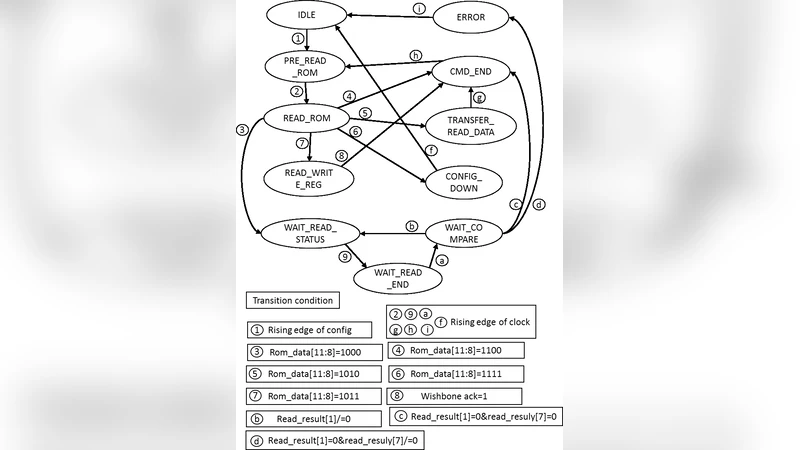

논문은 CBM(Compressed Baryonic Matter) 실험의 데이터 처리 보드(DPB) 계층에서 핵심적인 역할을 하는 AFCK(AMC FMC Carrier Kintex) 보드의 I2C 관리 구조를 상세히 분석한다. 먼저, IPBus가 정상 동작하기 위해서는 I2C 버스 멀티플렉서 선택, 125 MHz 클럭 교차 스위치 설정, EUI‑48 주소를 보유한 EEPROM에서 MAC 주소 획득 등 몇 가지 필수 장치가 올바르게 초기화되어야 함을 강조한다. 이를 위해 설계자는 두 개의 I2C 컨트롤러를 배치하였다. 하나는 전원 인가 시 자동 리셋에 의해 활성화되는 초기화 전용 컨트롤러이며, ROM에 16 bit 형식의 명령어 시퀀스를 저장해 FSM으로 순차 실행한다. 명령어 비트 배치는 버스 번호(3비트), 읽기/쓰기 플래그(1비트), 레지스터 포트(4비트), 데이터(8비트)로 구성되어 있어 다양한 I2C 장치에 대한 레지스터 접근을 단일 흐름으로 구현한다. 초기화가 완료되면 컨트롤러는 자동 전환 로직을 통해 IPBus‑I2C 마스터 코어로 스위치한다. 이 마스터는 Wishbone 인터페이스를 제공하므로 IPBus 슬레이브와 직접 연결될 수 있다. IPBus‑I2C 마스터는 프리스케일 레지스터, 제어 레지스터, 전송/수신 레지스터, 명령/상태 레지스터 등 네 개의 8 bit 레지스터를 통해 SCL 주파수 설정, 장치 주소 전송, 데이터 전송 및 상태 확인을 수행한다.

소프트웨어 측면에서는 IPBus 클라이언트(파이썬/C++)가 Ethernet을 통해 Wishbone 버스에 접근하고, 이를 통해 I2C 마스터 레지스터를 읽·쓰는 방식으로 모든 I2C 장치를 실시간으로 제어한다. 특히, EEPROM에서 읽은 MAC 주소를 IPBus 초기화 단계에서 전달함으로써 네트워크 연결성을 보장하고, 클럭 교차 스위치를 통해 1 GbE 및 SGMII 인터페이스에 필요한 125 MHz 클럭을 정확히 라우팅한다. 또한, FMC 보드에 탑재된 프로그래머블 크리스털과 추가 I2C 장치도 동일한 경로로 구성·제어 가능하도록 설계되어, 보드 확장성을 크게 향상시킨다.

검증 결과, 제안된 초기화 모듈은 전원 인가 후 자동으로 모든 필수 I2C 장치를 설정하고, IPBus 연결이 성공적으로 이루어짐을 확인하였다. 이후 IPBus를 통한 I2C 레지스터 조작은 실시간 모니터링 및 파라미터 튜닝에 사용될 수 있었으며, 전체 시스템이 CBM DPB 설계 요구사항을 충족함을 입증하였다. 이와 같이 하드웨어‑소프트웨어 공동 설계는 복잡한 DAQ 환경에서 신뢰성 높은 저속 제어 인프라를 제공한다는 점에서 의미가 크다.

댓글 및 학술 토론

Loading comments...

의견 남기기