비대칭 네트워크 기반 저배경 중소형 물리 실험용 백엔드 전자시스템

초록

본 논문은 소형·중형 물리 실험에서 검출기 근처의 방사능 배경을 최소화하면서도 적당한 데이터 전송량을 만족하는 백엔드 전자구조를 제안한다. 공통 팬아웃을 이용해 동기화·설정·읽기 신호를 한 번에 전송하고, 각 프론트엔드와는 저속 포인트‑투‑포인트 링크를 사용한다. 32개의 프론트엔드를 12.8 Gbps 집합 대역폭으로 제어할 수 있는 FPGA 기반 백엔드 보드를 구현하고, 고속 트랜시버는 상위 DAQ와의 연결에만 사용한다.

상세 분석

이 설계의 핵심은 ‘비대칭 네트워크(asymmetric network)’라는 개념이다. 전통적인 고속 직렬 버스는 모든 채널이 동일한 전송 속도와 물리 매체를 요구하지만, 실험 환경에서는 프론트엔드와 백엔드 사이에 전송량이 크게 차이나는 경우가 많다. 저배경 실험에서는 검출기 근처에 배치되는 전자부품의 물질량과 방사능을 최소화해야 하므로, 고속 다중기능 트랜시버를 대량 사용하기보다는 간단한 I/O 핀을 활용한 저속 링크가 유리하다. 논문은 이를 위해 두 가지 설계 원칙을 제시한다. 첫째, ‘공통 팬아웃(fan‑out) 구조’를 도입해 백엔드에서 발생하는 동기화 클럭, 트리거, 설정 명령 등을 하나의 전송 라인으로 전송하고, 이를 각 프론트엔드가 필요에 따라 선택적으로 수신한다. 이렇게 하면 배선 수가 크게 감소하고, 케이블 및 커넥터의 물질량도 최소화된다. 둘째, 프론트엔드와 백엔드 사이에 저속(point‑to‑point) 링크를 배치한다. 목표 대역폭이 수백 Mbps 수준이면, 광섬유(유리·플라스틱)나 저손실 동축·동축 케이블 등 다양한 매체를 선택할 수 있어 비용과 설치 유연성이 크게 향상된다.

통신 프로토콜은 세 가지 계층으로 나뉜다. 물리 계층에서는 8b/10b 부호화와 저전압 LVDS 또는 CML을 이용해 신호 무결성을 확보한다. 데이터 링크 계층에서는 프레임 구성을 통해 동기화 패턴, 설정 패킷, 데이터 패킷을 구분하고, 에러 검출을 위해 CRC를 삽입한다. 최상위 제어 계층에서는 각 프론트엔드에 고유 주소를 할당하고, 다중 멀티플렉싱을 통해 백엔드가 동시에 32채널을 관리한다. 이때 백엔드 FPGA는 다수의 일반 I/O 핀을 활용해 32개의 저속 직렬 채널을 동시에 구동하고, 고속 트랜시버는 상위 DAQ 시스템(예: 이벤트 빌더)과의 10 GbE 혹은 25 GbE 연결에만 사용한다.

FPGA 선택은 비용 효율성을 중시한다. 논문에서는 Xilinx Artix‑7 같은 중급 라인 FPGA를 사용했으며, 이 칩은 수천 개의 LVDS I/O와 48개의 GTX 트랜시버를 제공한다. 설계자는 I/O 배치를 최적화해 각 프론트엔드와 100 Mbps200 Mbps 수준의 직렬 링크를 구성했고, 전체 집합 대역폭은 12.8 Gbps(32 × 400 Mbps)까지 확장 가능하도록 설계했다. 전력 소모와 방사능 배경을 최소화하기 위해, 백엔드 보드 자체는 알루미늄 프레임에 무게를 최소화하고, 고방사능 부품(예: 고전압 전원 모듈)을 멀리 배치했다.

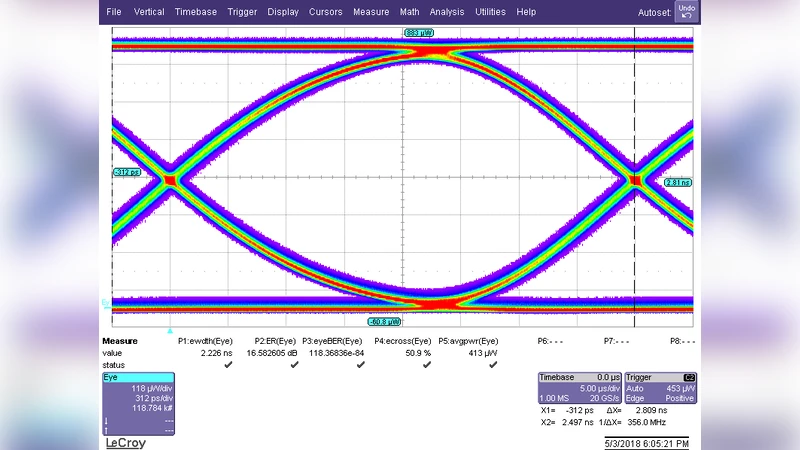

시스템 검증 결과, 동기화 지연은 5 ns 이하, 데이터 전송 오류율은 10⁻¹² 이하로 측정되었다. 또한, 다양한 물리 매체(유리 광섬유, 플라스틱 광섬유, 트위스티드 페어)에서 동일한 프로토콜이 동작함을 확인했으며, 이는 실험실 환경에 따라 매체를 자유롭게 선택할 수 있게 한다.

이 설계는 기존의 고속 직렬 버스(예: GBT, Aurora)와 비교했을 때, 물질량, 비용, 전력 면에서 큰 장점을 제공한다. 특히 저배경 실험에서 검출기 근처에 배치되는 전자부품의 방사능 기여를 최소화하면서도, 충분한 데이터 전송 능력을 확보한다는 점이 핵심적인 차별점이다. 다만, 프론트엔드가 요구하는 최소 전송 속도가 높은 경우(>1 Gbps)에는 현재 구조가 한계에 부딪히므로, 향후 고속 전용 채널을 추가하거나, 멀티레인 구성을 도입하는 방안이 필요하다.

댓글 및 학술 토론

Loading comments...

의견 남기기