FPGA 구현 파이프라인 디지털 슬라이싱 무곱셈기 레이더 2 2 DIF SDF FFT 버터플라이

본 논문은 고속 무선 통신에 필수적인 FFT 연산의 병목을 해소하기 위해, Radix‑2² DIF SDF 구조에 디지털 슬라이싱 기반 무곱셈기(Multiplier‑less) 방식을 적용한 파이프라인 버터플라이 설계를 제안한다. 입력 데이터를 4비트씩 4개의 블록으로 분할하여 병렬 연산을 수행하고, 미리 계산된 곱셈 결과를 ROM에 저장함으로써 전통적인 곱셈기를 제거한다. Xilinx Virtex‑II XC2V500‑6‑FG456 FPGA에 구현…

저자: Yazan Samir Algnabi, Rozita Teymourzadeh, Masuri Othman

본 논문은 무선 통신 시스템에서 핵심적인 역할을 하는 고속 푸리에 변환(FFT)의 성능 향상을 목표로, FPGA에 구현 가능한 파이프라인형 디지털 슬라이싱 무곱셈기 기반 Radix‑2² DIF(Single‑Path Delay Feedback) SDF 버터플라이 구조를 제안한다. 연구 배경으로는 기존 FFT 구현에서 복소수 곱셈이 가장 큰 연산 병목이며, 특히 고속 실시간 처리에서는 전통적인 곱셈기(DSP 블록) 사용이 전력·면적·속도 측면에서 제한적이라는 점을 지적한다.

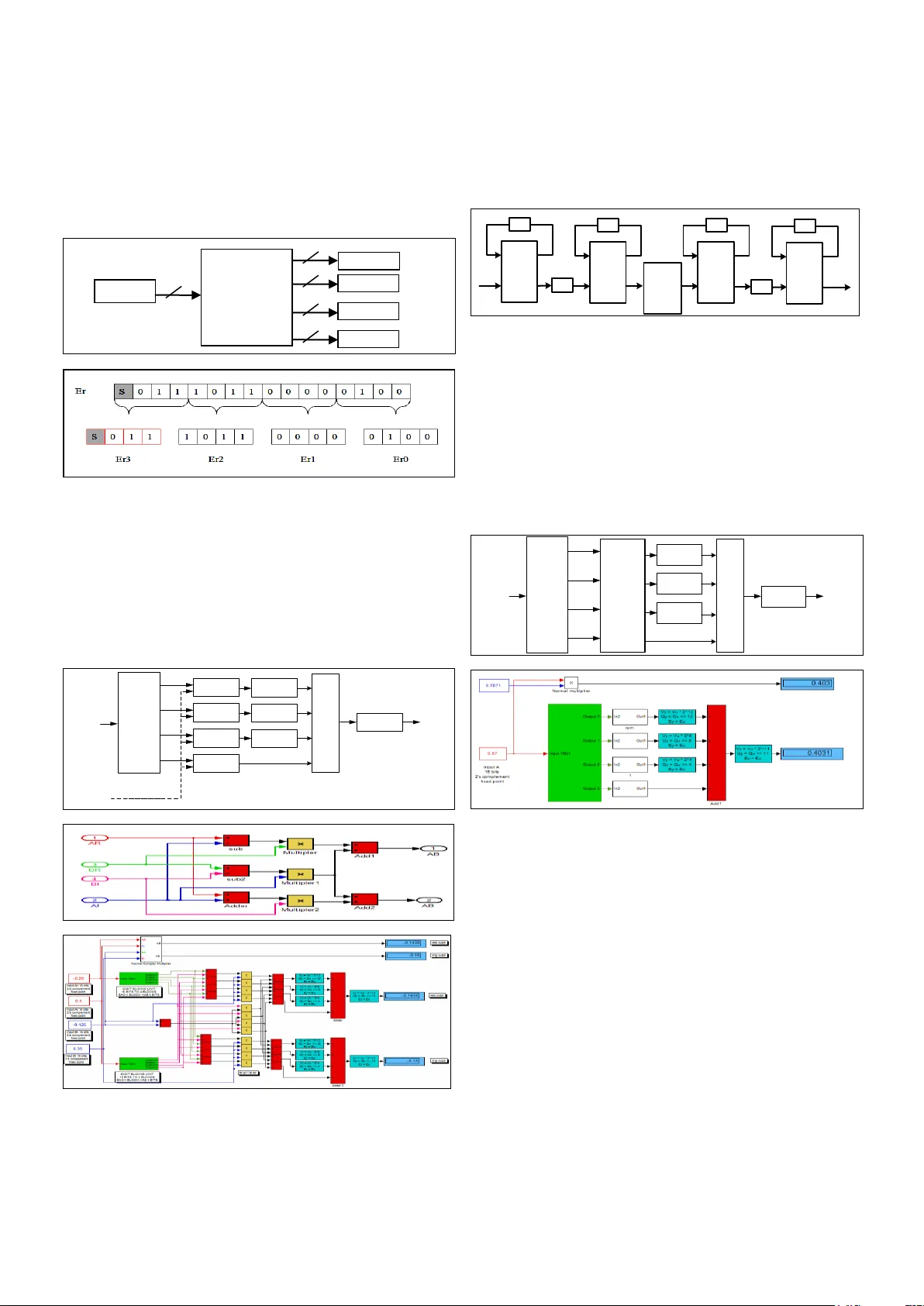

논문은 먼저 Radix‑2² DIF SDF 알고리즘을 소개한다. 이 알고리즘은 Radix‑2와 Radix‑4의 장점을 결합한 형태로, 2‑point 버터플라이 연산을 두 단계에 걸쳐 수행하면서 –j 회전(실수·허수 교환 및 부호 반전)을 효율적으로 처리한다. 구조는 Butterfly I, Butterfly II, 그리고 복소수 곱셈기 세 부분으로 나뉘며, 피드백 레지스터를 이용해 연속적인 데이터 스트림을 실시간으로 처리한다.

핵심 기여는 복소수 곱셈기를 디지털 슬라이싱 무곱셈기로 대체한 점이다. 입력 데이터(16비트 2’s complement)와 트윌 팩터(16비트 고정소수점)를 각각 4비트 블록 4개로 분할한다. 각 블록은 2⁴=16가지 경우의 수만을 가질 수 있으므로, 16개의 곱셈 결과를 미리 계산해 ROM에 저장한다. 실제 연산 시에는 입력 블록을 해당 ROM 주소로 매핑하고, 시프트 연산(12, 8, 4, 0 비트)과 가산·뺄셈을 통해 최종 16비트 결과를 재구성한다. 이 과정은 전통적인 4실수 곱셈기와 1덧셈·1뺄셈 회로를 사용하는 방식에 비해 회로 면적과 연산 지연을 크게 감소시킨다.

설계 단계에서는 MATLAB을 이용해 디지털 슬라이싱 알고리즘을 검증하고, Verilog HDL로 전체 파이프라인을 기술하였다. Xilinx ISE 환경에서 XST 합성 툴을 사용해 Virtex‑II XC2V500‑6‑FG456 FPGA에 구현하였다. 실험 결과, 제안된 파이프라인 디지털 슬라이싱 버터플라이는 최대 클럭 주파수 555.75 MHz를 달성했으며, 등가 게이트 수는 32,146으로 기존 Radix‑2² DIF SDF 버터플라이(최대 200.102 MHz, 약 70 k게이트) 대비 2.7배 이상의 속도 향상과 면적 절감을 보였다. 또한, 기존 FPGA 내장 고속 곱셈기(최대 221.140 MHz)와 비교했을 때도 약 2.5배 빠른 성능을 기록하였다.

논문의 장점은 다음과 같다. 첫째, 곱셈기 회로를 완전히 제거함으로써 DSP 블록 사용을 최소화하고, 남은 로직을 고속 파이프라인에 집중할 수 있다. 둘째, ROM 기반 사전 계산 방식은 트윌 팩터가 고정된 FFT에 최적화되어 메모리 사용량이 제한된 환경에서도 효율적으로 동작한다. 셋째, 파이프라인 구조와 피드백 레지스터를 이용해 연속적인 데이터 스트림을 실시간으로 처리할 수 있어, 저지연 통신 시스템에 적합하다.

반면 제한점으로는 입력 데이터와 트윌 팩터가 16비트 고정소수점이라는 전제에 의존한다는 점이다. 다른 정밀도나 부동소수점 포맷을 적용하려면 추가 설계가 필요하다. 또한, 트윌 팩터가 가변되는 가변‑길이 FFT에서는 ROM 내용을 재구성해야 하므로 유연성이 다소 떨어진다. 시프트·가산 기반 재구성 과정에서 발생할 수 있는 정밀도 손실을 보정하기 위한 스케일링 로직이 추가되어 설계 복잡성이 증가한다.

결론적으로, 이 연구는 FPGA 기반 고속 FFT 구현에서 곱셈 연산을 제거하고 파이프라인 효율을 극대화하는 실용적인 방법을 제시한다. 디지털 슬라이싱 무곱셈기와 Radix‑2² DIF SDF 구조의 결합은 5G/6G 무선 통신, 레이더 신호 처리, 실시간 영상 분석 등 고대역폭 실시간 DSP 응용 분야에 큰 파급 효과를 기대할 수 있다. 향후 연구에서는 다양한 비트 폭 지원, 가변‑길이 FFT 적용, 그리고 ASIC 구현을 통한 전력 효율 최적화가 제안된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기