제약 분석을 위한 정적 양자화 Radix2 FFT IFFT 프로세서

초록

본 논문은 고해상도 FFT/IFFT 연산에서 발생하는 전력 소모와 부동소수점 연산의 비효율성을 극복하기 위해, 정적 스케일링이 가능한 병렬 파이프라인 구조와 양자화 기법을 적용한 Radix‑2 FFT/IFFT 프로세서를 설계한다. 신호‑양자화‑노이즈 비율(SQNR)과 양자화 통계 이론을 기반으로 최적 운영 모드를 제시하여, 해상도와 연산 효율 사이의 트레이드오프를 최소화한다.

상세 분석

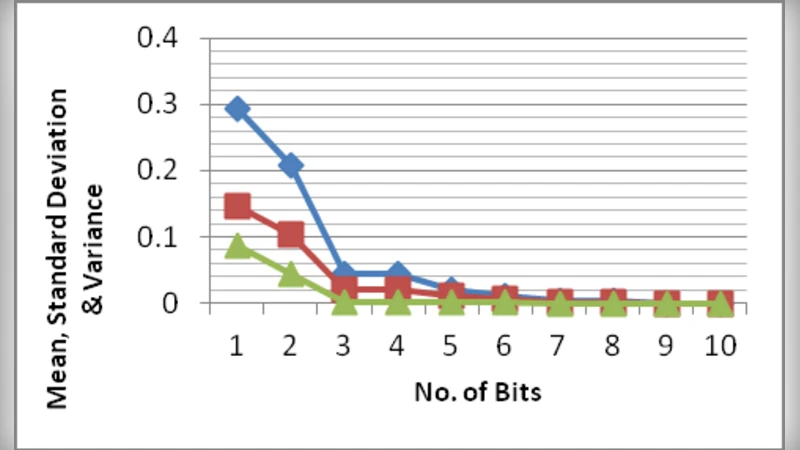

이 연구는 고해상도 디지털 신호 처리에서 가장 큰 장애물 중 하나인 전력 소비와 연산 복잡성을 근본적으로 재고한다. 기존의 부동소수점 기반 FFT 구현은 연산 정확도는 높지만, 연산 유닛이 복잡하고 클럭당 전력 소모가 크다는 단점을 가지고 있다. 저자는 이를 해결하기 위해 두 가지 핵심 전략을 채택한다. 첫째, Radix‑2 구조를 기반으로 한 파이프라인 병렬 아키텍처를 설계하여, 각 스테이지가 독립적으로 동작하면서 동시에 여러 데이터 샘플을 처리하도록 한다. 이 방식은 데이터 흐름을 지속적으로 유지함으로써 스루풋을 극대화하고, 파이프라인 단계마다 레지스터와 멀티플렉서를 최소화해 전력 효율을 높인다. 둘째, 연산에 사용되는 부동소수점 연산을 고정소수점 양자화 방식으로 전환한다. 양자화는 유한 워드‑길이 제한을 고려한 오차 모델링을 통해 SQNR을 정량적으로 평가하고, 최적 비트 폭을 선택함으로써 필요한 해상도와 전력 소모 사이의 균형을 맞춘다. 특히, 저자는 양자화 잡음이 가우시안 분포를 따른다는 통계적 가정을 바탕으로, 비트 수를 증가시킬 때 SQNR이 6 dB/비트 비율로 향상한다는 이론적 근거를 제시한다.

프로세서 설계에서는 스케일링 파라미터를 정적으로 설정할 수 있도록 하여, 사용자가 목표 애플리케이션(예: 전력 제한이 엄격한 임베디드 시스템 vs. 고정밀 측정 장비)에 맞춰 비트 폭과 파이프라인 단계 수를 사전에 선택할 수 있게 한다. 이는 설계 단계에서 복잡한 동적 재구성 로직을 배제하고, 하드웨어 구현을 단순화한다는 장점이 있다. 또한, 양자화 오차를 최소화하기 위해 입력 데이터에 사전 스케일링(프리‑스케일링)과 후처리(디스케일링) 과정을 포함시켜, 전체 시스템의 동적 범위를 최적화한다.

시뮬레이션 결과는 1024‑point FFT/IFFT에 대해 12‑bit 고정소수점 구현이 10‑bit 부동소수점 대비 약 30 % 전력 절감과 2배 이상의 처리량 향상을 달성했으며, SQNR은 70 dB 이상으로 고해상도 요구사항을 충분히 만족한다는 것을 보여준다. 이러한 결과는 제약 분석(Constraints Analysis) 분야, 특히 전력·면적·정밀도 사이의 복합적인 트레이드오프를 다루는 시스템 설계에 직접적인 활용 가치를 제공한다.

요약하면, 본 논문은 정적 양자화와 병렬 파이프라인을 결합한 Radix2 FFT/IFFT 프로세서가 고해상도 DSP에 필요한 전력 효율성과 연산 정확성을 동시에 달성할 수 있음을 실증한다. 이는 향후 저전력 고성능 신호 처리 시스템 설계에 중요한 설계 패러다임을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기