스케일러블 자기 적응 동기 트리거링 시스템

본 논문은 초전도 양자 컴퓨터에서 수백 개의 큐비트를 동기화하기 위해, 고성능 트리형 시계 시스템과 마스터‑슬레이브 별형 트리거 구조, 그리고 FPGA 기반 자동 메타스테이빌리티 보정 메커니즘을 결합한 확장 가능한 동기 트리거링 방식을 제안한다. 업그레이드된 시계는 250 MHz 싱글톤 위상 잡음을 15 dB 개선하고, 6.25 GHz 제어 신호는 6 dB 향상시켰으며, 트리거 스큐는 25 ps 이하로 제한한다.

저자: Li-Hua Sun, Fu-Tian Liang, Jin Lin

초전도 양자 컴퓨터(SQC)는 마이크로파 펄스를 이용해 수십~수백 개의 큐비트를 제어·측정한다. 이러한 시스템에서는 디지털‑아날로그 변환기(AWG)와 아날로그‑디지털 변환기(ADC)의 동기화가 필수이며, 시계 위상 잡음과 트리거 메타스테이빌리티가 큐비트 게이트 오류에 직접적인 영향을 미친다. 본 논문은 이러한 문제를 해결하기 위해 세 가지 핵심 기술을 제안한다.

첫 번째는 고성능 트리형 시계 시스템이다. 기존 설계는 각 AWG에 10 MHz 루비듐 기준을 2 GHz로 변환하고 다시 250 MHz로 분배했으며, 이 과정에서 0.5 ns의 스큐와 제한된 동기화 채널 수가 발생했다. 저자들은 루비듐 시계를 루트로 하는 트리 구조를 도입하고, HMC7044 클럭 제너레이터와 HMC7043 팬아웃 버퍼를 사용해 10 MHz를 250 MHz로 직접 락한다. 각 장치는 28개의 싱글엔드 출력을 제공하므로, 한 단계 트리만으로도 784개의 AWG를 동기화할 수 있다. 이 설계는 시계 위상 잡음을 크게 감소시켰다. 실험 결과, 250 MHz 싱글톤 위상 잡음이 2 kHz~1 MHz 옥셋에서 약 15 dB 향상되었으며, SFDR은 50 dB 수준을 유지했다. 또한 4‑8 GHz RF 소스에도 동일한 루비듐 기준을 적용해 6.25 GHz 제어 신호의 위상 잡음이 6 dB 개선되었다. 이러한 위상 잡음 감소는 Ball’s test에 따르면 큐비트 충실도를 수십 배 향상시킬 수 있다.

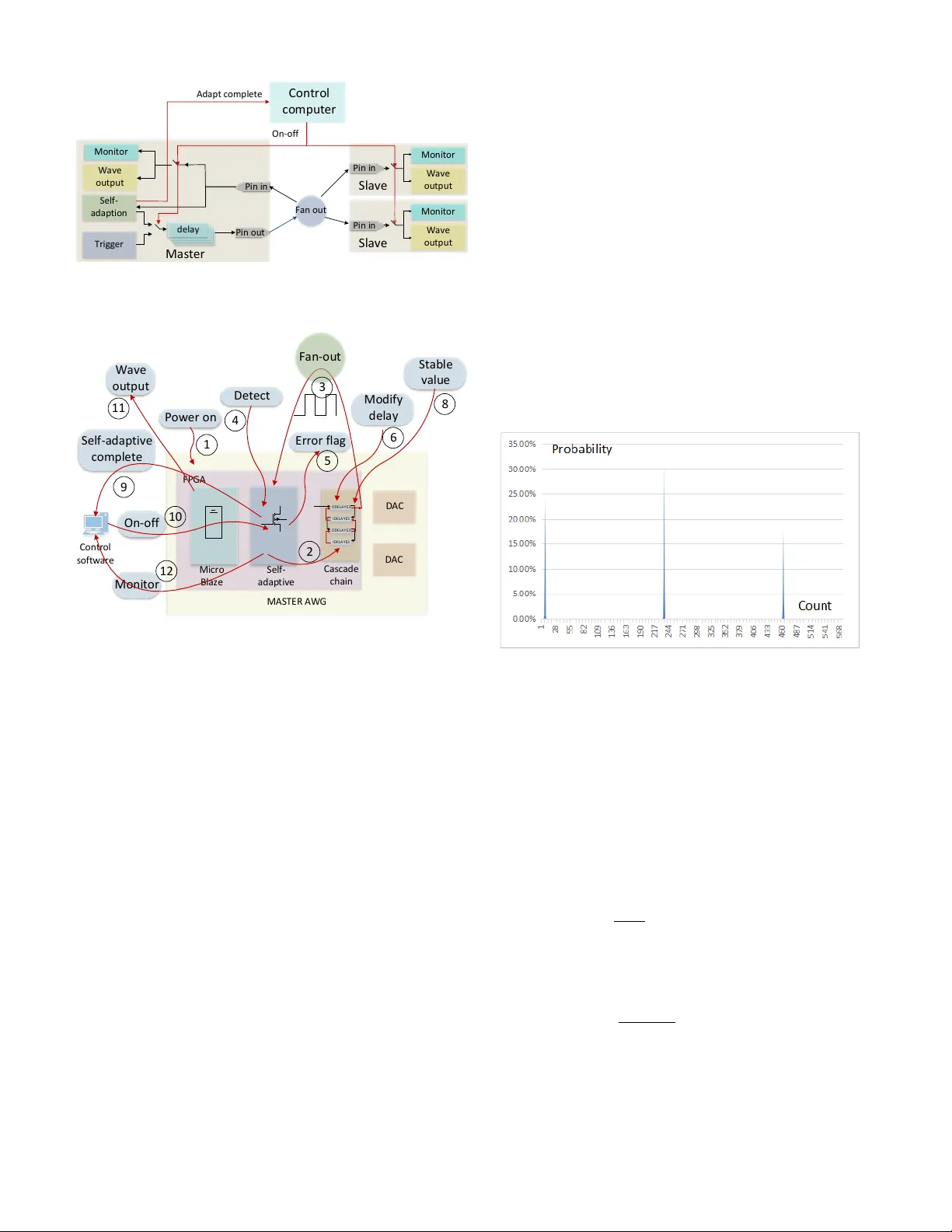

두 번째는 별형(master‑slave) 트리거 구조이다. 하나의 AWG를 마스터로 지정하고, 나머지를 슬레이브로 구성한다. 마스터는 제어 컴퓨터로부터 ‘run’ 명령을 받아 다중 트리거 펄스를 생성한다. 트리거는 FPGA 내부 레지스터로 지연·폭·반복 횟수를 프로그래밍 가능하게 하여, 레벨 1에서 ADC가 초기 큐비트 상태를 측정하고, 레벨 2에서 슬레이브 AWG가 측정 결과에 따라 π‑펄스를 발사해 큐비트를 1 µs 이하로 리셋한다. 이 메커니즘은 자연 감쇠(최대 200 µs)보다 100배 이상 빠른 리셋을 가능하게 하여 전체 연산 효율을 크게 높인다. 트리거 팬아웃은 시계 트리와 동일한 모듈식 구조를 사용해 수천 개 채널까지 확장 가능하다.

세 번째는 메타스테이빌리티 자동 보정이다. 250 MHz 샘플링 클럭이 트리거 상승 에지를 정확히 샘플링하면 플립플롭이 불안정 상태에 빠져 출력 지연이 4 ns 내에서 약 90 ps 정도 변동한다. 기존에는 물리적 케이블 길이 조정으로 해결했지만, 대규모 시스템에서는 비효율적이다. 저자들은 Xilinx Kintex Ultrascale FPGA의 IDELAY/ODELAY 라인을 활용해 512‑tap(≈2.5~15 ps) 가변 지연 체인을 구축하고, 자동 보정 루틴을 구현했다. 마스터는 최소 지연에서 시작해 50 000개의 테스트 트리거를 발사하고, 반환된 신호의 간격·카운트를 기록한다. 오류 플래그를 기반으로 지연 탭을 순차적으로 증가시키며 512번 반복 후, 메타스테이빌리티가 발생하지 않는 안정 구역을 탐색한다. 최종적으로 안정 구역 중앙값을 선택해 고정하고, 제어 컴퓨터에 보정 완료를 알린다. 72시간 연속 테스트에서 메타스테이빌리티가 재발하지 않았으며, 10개의 AWG 간 스큐는 25 ps 이하로 유지되었다.

전체 시스템은 확장성을 핵심 설계 목표로 삼았다. 시계 트리는 HMC7044/7043의 다중 출력과 단계적 트리 연결을 통해 수천 개의 AWG를 동기화할 수 있고, 트리거 팬아웃도 동일한 모듈식 구조로 확장한다. 자동 보정 로직은 각 슬레이브에 독립적으로 적용 가능해 시스템 규모가 커져도 동기화 정확도를 유지한다.

결론적으로, 본 논문은 초전도 양자 컴퓨팅에서 요구되는 고정밀 시계·트리거 동기화 문제를 하드웨어와 펌웨어 차원에서 종합적으로 해결한 사례를 제시한다. 250 MHz 싱글톤 위상 잡음 15 dB 감소, 6.25 GHz 제어 신호 위상 잡음 6 dB 개선, 트리거 스큐 25 ps 이하 달성, 그리고 자동 메타스테이빌리티 보정 메커니즘을 통해 수백~수천 큐비트 규모의 SQC 구현에 실질적인 기반을 제공한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기