고성능 확장 가능한 초전도 양자 컴퓨팅용 임의 파형 발생기

초록

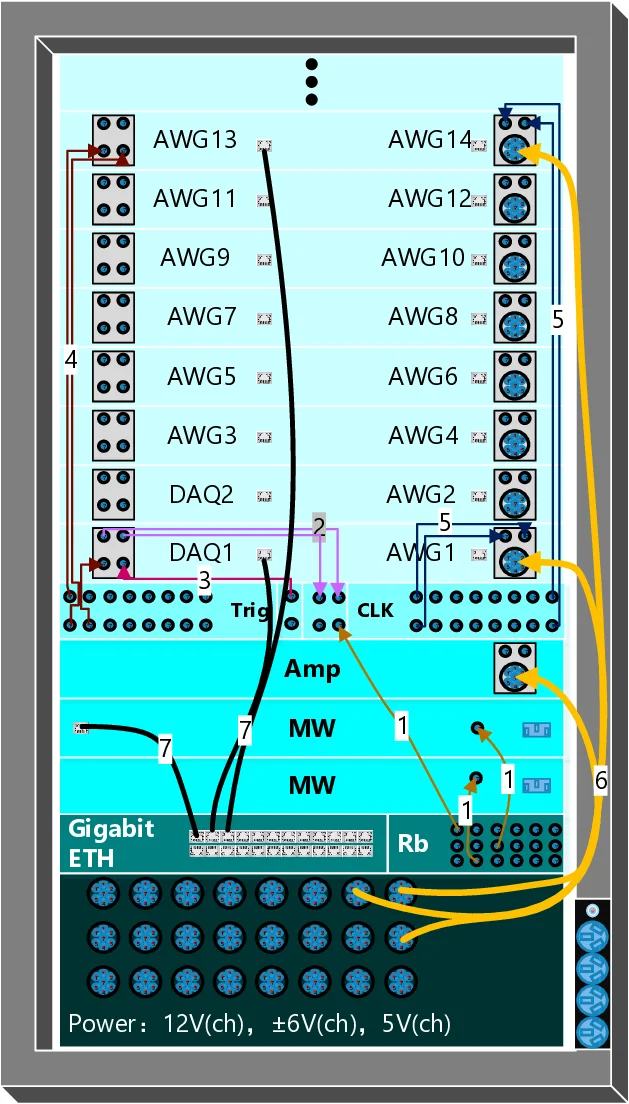

본 논문은 2 GSPS·16 bit DAC 기반의 임의 파형 발생기(AWG)를 설계·구현하고, 이를 금속 플레이트에 통합해 고밀도 확장성을 확보하였다. FPGA 기반 시퀀스 제어기로 채널 간 10 ps 수준의 동기화와 2 LSB 이하의 INL/DNL을 달성했으며, 상용 1 GSPS·14 bit AWG 대비 큐비트 T₂*가 33 % 향상된 결과를 보였다.

상세 분석

이 연구는 초전도 양자 컴퓨터의 제어 요구사항을 충족시키기 위해 기존 상용 AWG의 한계를 정확히 분석하고, 맞춤형 하드웨어·펌웨어 설계를 통해 해결책을 제시한다. 먼저, 양자 비트는 수십 개에서 수백 개로 확장될 경우 채널 수가 급증하고, 각 채널 간 동기화 정확도가 피코초 수준이어야 한다는 점을 강조한다. 이를 위해 저자들은 Xilinx FPGA와 두 개의 2 GSPS·16 bit DAC을 결합한 모듈을 설계했으며, JESD204B 프로토콜을 이용해 160 Gbps의 고속 직렬 전송을 구현하였다. 고속 데이터 전송과 동시에 250 MHz 외부 클럭을 모든 모듈에 동일하게 분배함으로써 전역 동기화를 확보하고, 10 ps 이하의 채널 간 지터와 100 ps 이하의 스큐를 실현하였다.

펌웨어 측면에서는 파형 메모리(WDM)와 시퀀스 메모리(SDM), 그리고 유한 상태 기계(FSM)로 구성된 시퀀스 출력 컨트롤러를 도입했다. 이 구조는 사전 페치(prefetch) 메커니즘을 통해 연속적인 파형 전환 시 발생할 수 있는 공백을 최소화하고, 최소 4 샘플 길이 제한을 두어 FSM이 충분히 준비 시간을 확보하도록 설계되었다. 결과적으로 복잡한 IQ 변조 파형이나 급격한 위상 전이 파형을 끊김 없이 출력할 수 있다.

성능 검증에서는 INL/DNL을 2 LSB 이하로 유지했으며, 주파수 10 MHz~250 MHz 구간에서의 위상 노이즈가 이론적인 6 dB/옥타브 감소를 따르는 것을 확인했다. 또한 SFDR 테스트에서 데이터시트와 일치하는 70 dB 이상의 동적 범위를 얻었다. 가장 중요한 양자 실험 검증에서는 동일한 큐비트 회로에 상용 1 GSPS·14 bit AWG와 자체 제작 2 GSPS·16 bit AWG를 교체 적용했을 때, T₂*가 각각 10 µs와 15 µs로 측정되어 33 %의 향상이 확인되었다. 이는 높은 샘플링 레이트와 비트 해상도가 양자 디코히런스 억제에 직접적인 영향을 미침을 실증한다.

전체 시스템은 1U 높이의 금속 플레이트에 FPGA, DAC, IQ 믹서, 파워 스플리터 등을 집적함으로써 공간 효율성을 극대화했으며, Ethernet 기반 TCP/IP 통신을 통해 다중 보드 간 확장성을 확보했다. 이러한 설계는 향후 수백 채널 규모의 양자 프로세서 제어에 필요한 모듈형 아키텍처로 활용될 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기