ATLAS sTGC 트리거 업그레이드용 p/sFEB 스캔 테스트 시스템 프로토타입

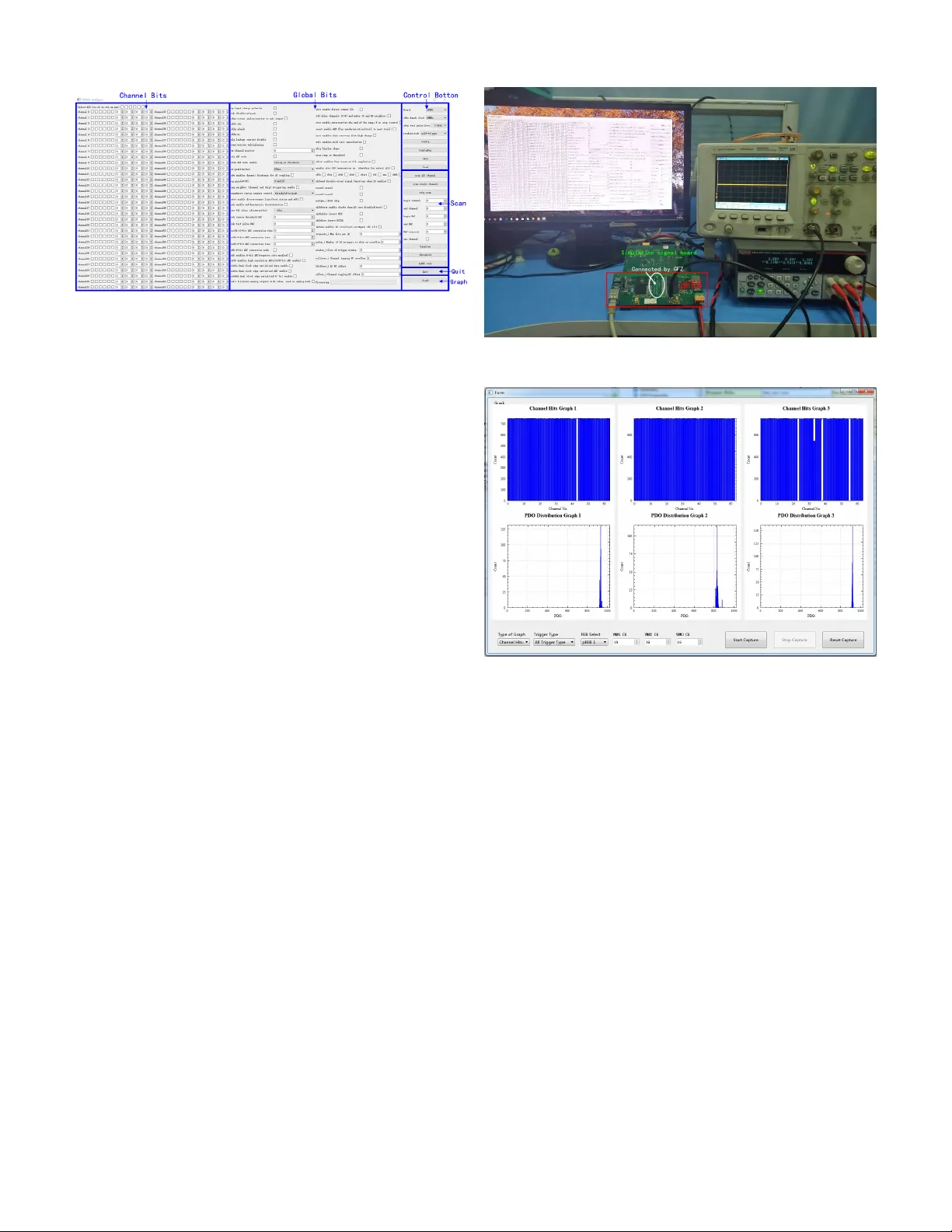

본 논문은 ATLAS Phase‑I sTGC 트리거 업그레이드에 사용되는 Pad Front End Board(pFEB)와 Strip Front End Board(sFEB)의 성능을 검증하기 위한 스캔 테스트 시스템 프로토타입을 소개한다. 시뮬레이션 신호 보드, FPGA 내장 XADC, 그리고 Qt 기반 PC GUI를 결합해 베이스라인, 임계값 DAC 보정, 내부 테스트 펄스 DAC 보정, 게인 및 죽은 채널 검사를 자동화한다. 이를 통해 200…

저자: Xinxin Wang, Feng Li, Shengquan Liu

본 논문은 ATLAS 실험의 Phase‑I sTGC 트리거 업그레이드에 사용되는 Pad Front End Board(pFEB)와 Strip Front End Board(sFEB)의 성능 검증을 위한 스캔 테스트 시스템 프로토타입을 상세히 기술한다. ATLAS는 현재 Large Hadron Collider(LHC)에서 운영 중이며, 내년부터 Small Wheel(SW) 교체를 통해 New Small Wheel(NSW)으로 업그레이드한다. NSW는 Small‑strip Thin Gap Chamber(sTGC)과 Micromegas(MM) 두 종류의 검출기로 구성되며, sTGC는 패드, 와이어, 스트립 3가지 읽기 채널을 갖는다. 패드 신호는 muon 트랙을 대략적으로 식별하고, 3‑out‑of‑4 코인시던스를 통해 트리거를 생성한다. 이 트리거는 스트립 읽기를 제어해 정확한 굽힘 좌표 측정을 가능하게 한다.

pFEB는 패드 신호를 수집·분석해 트리거를 생성하고, sFEB는 이 트리거를 받아 ROI(Region‑of‑Interest)를 정의해 스트립 데이터를 읽는다. 두 보드 모두 VMM3 ASIC을 사용해 64개의 아날로그 채널을 디지털 신호로 변환하고, 트리거 데이터와 원시 히트 데이터를 출력한다. 약 2000개의 p/sFEB가 생산될 예정이며, 실제 sTGC에 장착하기 전에 모든 보드의 전기적·기능적 특성을 검증해야 한다.

검증 항목은 베이스라인 전압, 임계값 DAC 보정, 내부 테스트 펄스 DAC 보정, 게인, 죽은 채널 여부 등이다. 기존에 오실로스코프를 이용해 수동으로 측정하던 방식은 채널 수와 보드 수가 많아 비효율적이었다. 이를 해결하기 위해 저자들은 다음과 같은 시스템을 설계·구현했다.

1. **시뮬레이션 신호 보드**: FPGA 기반 보드로, GFZ(10 × 30) 커넥터를 통해 p/sFEB에 256 ~ 512개의 테스트 펄스를 제공한다. 펄스의 전압, 폭, 주기 등을 프로그래밍 가능하며, VMM3 내부에서도 조정 가능한 테스트 펄스를 동시에 사용할 수 있다.

2. **FPGA XADC**: Kintex‑7 FPGA에 내장된 12‑bit XADC를 활용해 아날로그 파라미터를 자동으로 샘플링한다. 베이스라인 전압, 임계값 DAC 출력, 내부 테스트 펄스 전압 등을 XADC 채널에 연결해 100회 이상 반복 측정 후 평균값을 구한다. 이를 통해 측정 정확도와 재현성을 확보한다.

3. **Qt 기반 멀티스레드 GUI**: C++와 Qt 프레임워크로 구현된 PC 소프트웨어는 Pcap 라이브러리를 통해 Gigabit Ethernet(GET)으로 FPGA와 통신한다. GUI는 설정 파일을 통해 VMM3의 1728비트 구성(bit polarity, gain, peak time, threshold 등)을 자동으로 전송하고, 실시간으로 히트 카운트, 채널별 전압 분포, 게인 곡선 등을 그래프로 표시한다. 멀티스레드 구조로 데이터 수집과 화면 표시를 분리해 GUI가 멈추는 현상을 방지한다.

시스템 구현 과정에서 저자들은 VMM3 3칩(총 192채널)을 동시에 테스트하도록 설계했으며, 각 ASIC은 64개의 선형 프론트엔드 채널을 갖는다. 시뮬레이션 신호 보드는 외부에서 제어 가능한 펄스와 VMM3 내부 테스트 펄스를 조합해 다양한 테스트 시나리오를 구현한다.

**시험 결과**는 다음과 같다. 베이스라인 스캔에서는 64채널 각각을 100번씩 측정해 평균값과 표준편차를 구했으며, 채널 간 변동이 ±0.5 mV 이내로 일관성을 보였다. 임계값 DAC 보정과 내부 테스트 펄스 DAC 보정 역시 설계 사양 범위 내에서 정확히 재현되었다. 히트 카운트 그래프를 통해 죽은 채널을 자동으로 식별했으며, 추가적인 검증 절차를 통해 오탐률을 최소화했다. 전체 테스트 과정은 보드당 수분 내에 완료되었으며, 기존 수시간에 걸리던 수동 측정에 비해 10배 이상 속도가 향상되었다.

**한계점 및 향후 과제**로는 XADC의 샘플링 레이트가 제한적이라 고속 펄스 형태(수 ns 수준)의 정밀 측정에 제약이 있다. 또한, 현재 시스템은 최대 3칩(192채널)만 지원하므로, 8칩(512채널) 구성을 지원하려면 FPGA 리소스와 Ethernet 대역폭을 재설계해야 한다. 시뮬레이션 신호 보드가 실제 sTGC 신호 파형을 완벽히 재현하지 못할 가능성이 있어, 최종 검증 단계에서 실제 detector와 연동한 테스트가 필요하다.

결론적으로, 본 논문은 대규모 전방 전자 보드(p/sFEB)의 품질 검증을 자동화하고, 측정 정확도와 효율성을 크게 향상시킨 스캔 테스트 시스템 프로토타입을 제시한다. 이 시스템은 ATLAS NSW 업그레이드 일정에 필수적인 검증 인프라로 활용될 것이며, 향후 다른 고에너지 물리 실험의 전자 시스템 검증에도 적용 가능할 것으로 기대된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기