CSNS μSR 스펙트로미터용 32채널 TDC 설계

본 논문은 중국 스팔레이션 중성자원(CSNS)에서 구축 중인 μSR 스펙트로미터의 양전자 비행시간 측정을 위해, Xilinx Virtex‑6 FPGA 하나에 32채널 타임‑투‑디지털 컨버터(TDC)를 구현한 설계와 시험 결과를 제시한다. 200 MHz의 16개 위상 이동 클럭을 이용해 312.5 ps의 타임베인을 달성하고, 16 bit 코스 카운터와 512‑깊이 히트 버퍼를 결합해 최대 327 µs의 측정 범위를 제공한다. 온도에 대한 민감도가…

저자: Fanshui Deng, Hao Liang, Bangjiao Ye

본 논문은 중국 스팔레이션 중성자원(CSNS)에서 진행 중인 μSR(뮤온 스핀 회전·이완·공명) 실험을 위한 핵심 계측 장치인 128채널 μSR 스펙트로미터의 일부인 32채널 타임‑투‑디지털 컨버터(TDC)를 설계·구현·시험한 내용을 다룬다. μSR은 뮤온 스핀을 이용해 물질 내부의 미세 자기 구조를 탐색하는 기술로, 전 세계적으로 ISIS, J‑PARC, PSI, TRIUMF 등에서 고성능 뮤온원을 운영하고 있다. 현재 중국에서는 CSNS에 새로운 뮤온원을 건설 중이며, 이에 맞춰 최초의 국내 μSR 스펙트로미터를 개발하고 있다.

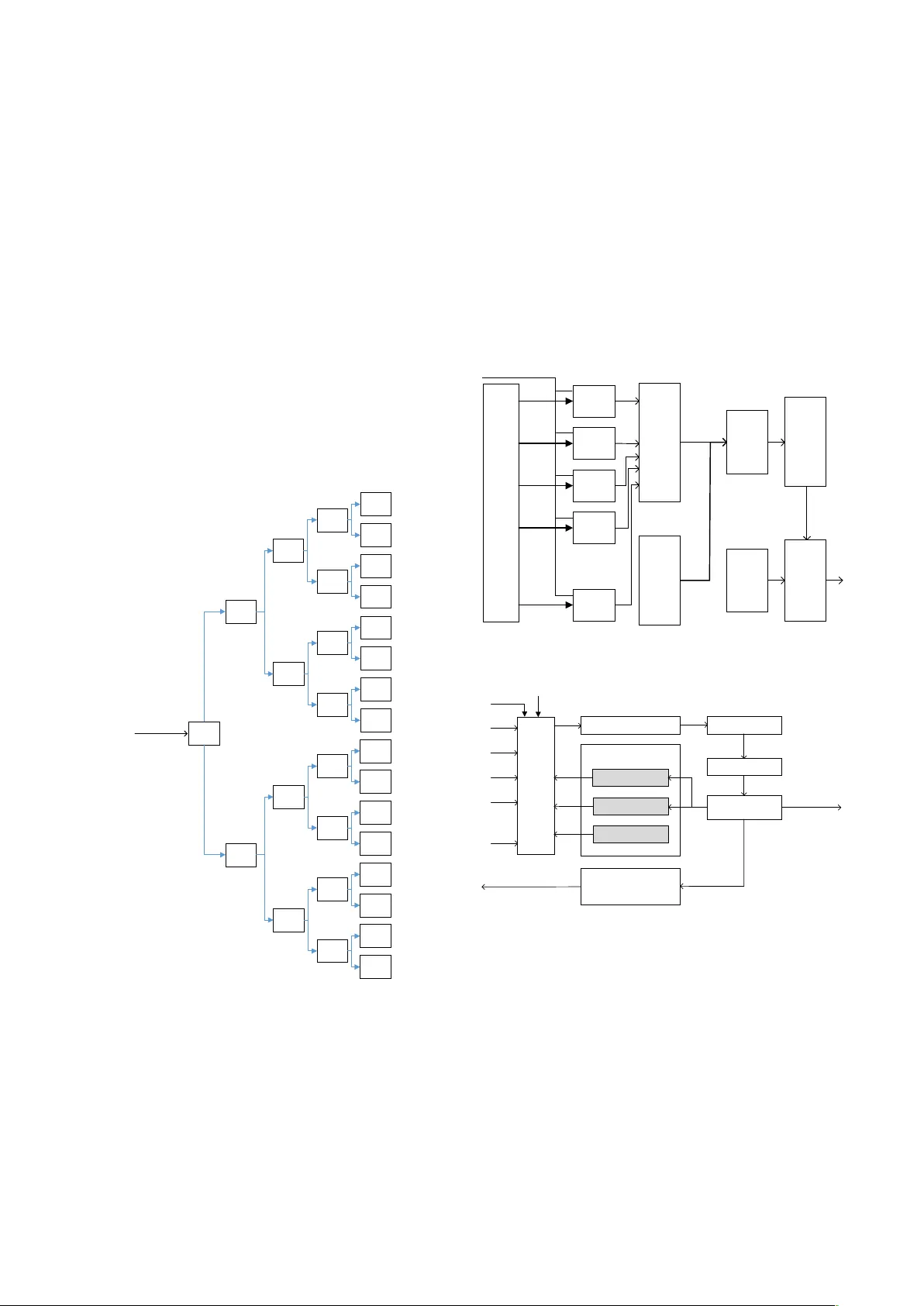

μSR 실험에서 핵심은 뮤온이 시료에 입사한 순간(시작 신호)과 뮤온 붕괴 시 발생하는 양전자가 검출기에서 포착되는 순간(정지 신호) 사이의 비행 시간을 정밀하게 측정하는 것이다. 이를 위해 저자들은 Xilinx Virtex‑6 FPGA 하나에 32채널 TDC를 구현하였다. 설계 방식은 크게 두 가지가 있는데, 하나는 지연 라인 기반 DDS(Delay‑Data Sampling)이고 다른 하나는 위상 이동 클럭 샘플링(SCS)이다. 본 설계는 리소스 절감과 제어 로직의 복잡성을 고려해 SCS 방식을 채택하였다.

클럭 생성은 외부 200 MHz 기본 클럭을 두 개의 PLL을 통해 400 MHz까지 증폭하고, 22.5° 위상 차이를 갖는 16개의 샘플링 클럭을 만든다. 입력 신호는 16개의 플립플롭에 동시에 연결되며, 8개는 상승 에지, 나머지 8개는 하강 에지에서 동작한다. 이렇게 하면 실제로는 16개의 등간격 샘플링이 이루어져 5 ns/16 = 312.5 ps의 타임베인이 확보된다.

시간 스큐를 최소화하기 위해 입력 라인을 4단계 LUT 뒤에 배치하고, 동일한 슬라이스 컬럼에 위치시켜 배치 제약을 가한다. LUT의 INIT 파라미터를 2’h2 로 설정해 입력을 그대로 전달하도록 함으로써, 신호 전파 지연을 수십 피코초 수준으로 억제한다. 이러한 설계는 FPGA 내부 라우팅 변동에 의한 비선형성을 크게 감소시켜, 실제 측정에서 높은 선형성을 확보한다.

코스 카운터는 200 MHz 클럭으로 구동되는 16‑bit 업카운터이며, 이는 327 µs(2¹⁶ × 5 ns)까지 연속 측정이 가능하도록 한다. 파인 카운터와 코스 카운터는 각각 히트 버퍼에 함께 저장되며, 버퍼 깊이는 512 엔트리로 설정돼 짧은 시간 내 다중 히트를 손실 없이 기록한다. 또한, 20 bit 타임 데이터와 26 bit 타임 태그, 8 bit 트리거 카운트를 포함한 54 bit 데이터를 64 bit 워드로 패키징해 FIFO에 적재하고, Gigabit Ethernet MAC/IP 코어를 통해 DAQ 시스템으로 전송한다.

채널 셀링 및 시간 윈도우 프로그래밍, 채널 셰일딩 기능을 통해 사용자는 관심 있는 채널과 시간 구간만 선택적으로 기록할 수 있다. 각 채널별 지연 보정은 LUT 기반 보정 테이블을 이용해 실시간으로 적용 가능하며, FPGA 내부 DAC와 연동된 셀프‑체크 회로가 주기적으로 인공 펄스를 생성해 시스템 상태를 검증한다.

시험은 Tektronix AFG3252C 듀얼 채널 펑션 제너레이터를 이용해 시작‑정지 펄스를 200 ps 간격으로 변화시키며 수행되었다. 측정된 FWHM은 최악 385.8 ps였으며, 통계적으로 √2 로 나누어 단일 채널 정밀도가 273 ps 이하임을 확인했다. 입력 간격에 대한 기대값과 측정값의 회귀 분석 결과 R²=0.99999989 로, 선형성이 거의 완벽에 가깝다. 온도 변화에 대한 실험에서도 정밀도 저하가 미미함을 보고하였다.

결론적으로, 본 설계는 312.5 ps 베인, 327 µs 측정 범위, 512‑깊이 히트 버퍼, 실시간 설정 및 캘리브레이션 기능을 갖춘 32채널 TDC를 FPGA 하나에 구현함으로써 μSR 실험에 필요한 고정밀·고채널·넓은 시간 범위 요구를 만족한다. 향후 128채널 전체 시스템에 적용하기 위해서는 동일한 구조를 복제하거나, 더 높은 정밀도를 위해 캐리 체인 기반 서브‑베인 보강을 고려할 수 있다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기