8비트 CMOS 우선순위 인코더 설계와 한계 극복을 위한 새로운 구조

본 논문은 1990년대 이후 제안된 8비트 CMOS 우선순위 인코더(PE)들을 45 nm 공정으로 동일하게 구현·시뮬레이션하여 전력, 지연, 면적을 공정적으로 비교한다. 기존 설계가 흔히 겪는 레이스 컨디션·전하 공유·고차 인코더 연쇄 불가능 등의 문제점을 분석하고, 3단계 룩어헤드와 액티브‑로우 제어를 결합한 새로운 PE 구조를 제안한다. 제안 회로는 레이스와 전하 공유를 완전히 제거하고, 높은 속도와 낮은 전력·면적을 유지하면서 상위 레벨 …

저자: Xiaoyu Wang, Yukang Feng

본 논문은 디지털 시스템에서 널리 사용되는 우선순위 인코더(PE)의 설계 현황을 1998년부터 2013년까지 발표된 8비트 CMOS 동적 PE들을 중심으로 종합적으로 검토한다. 먼저, 기존 연구들을 정리하면서 각 설계가 목표로 한 전력 절감, 지연 최소화, 트랜지스터 수 감소라는 세 가지 핵심 메트릭을 소개한다. Delgado‑Frias와 Nyathi(1998)는 순차적인 토큰 전달 방식으로 O(n) 지연을 초래했으며, Wang·Huang(2002)은 4‑bit 블록 두 개를 병렬로 연결하고 내부 룩어헤드 신호를 도입해 지연을 개선했지만 pMOS 중심 설계와 nMOS 중심 설계 두 가지 변형만을 제시했다. Kun 등(2004)은 8‑bit 모듈에 내부 룩어헤드 없이 단일 블록을 구현했으며, Huang·Chang(2010)과 Panc hal 등(2013)은 액티브‑하이·액티브‑로우 로직을 적용해 전력·지연을 최적화하려 했다. Mohanraj 등(2012)은 전력·지연·면적을 동시에 고려한 설계를 제안했지만 레이스 컨디션과 전하 공유에 대한 언급이 부족했다.

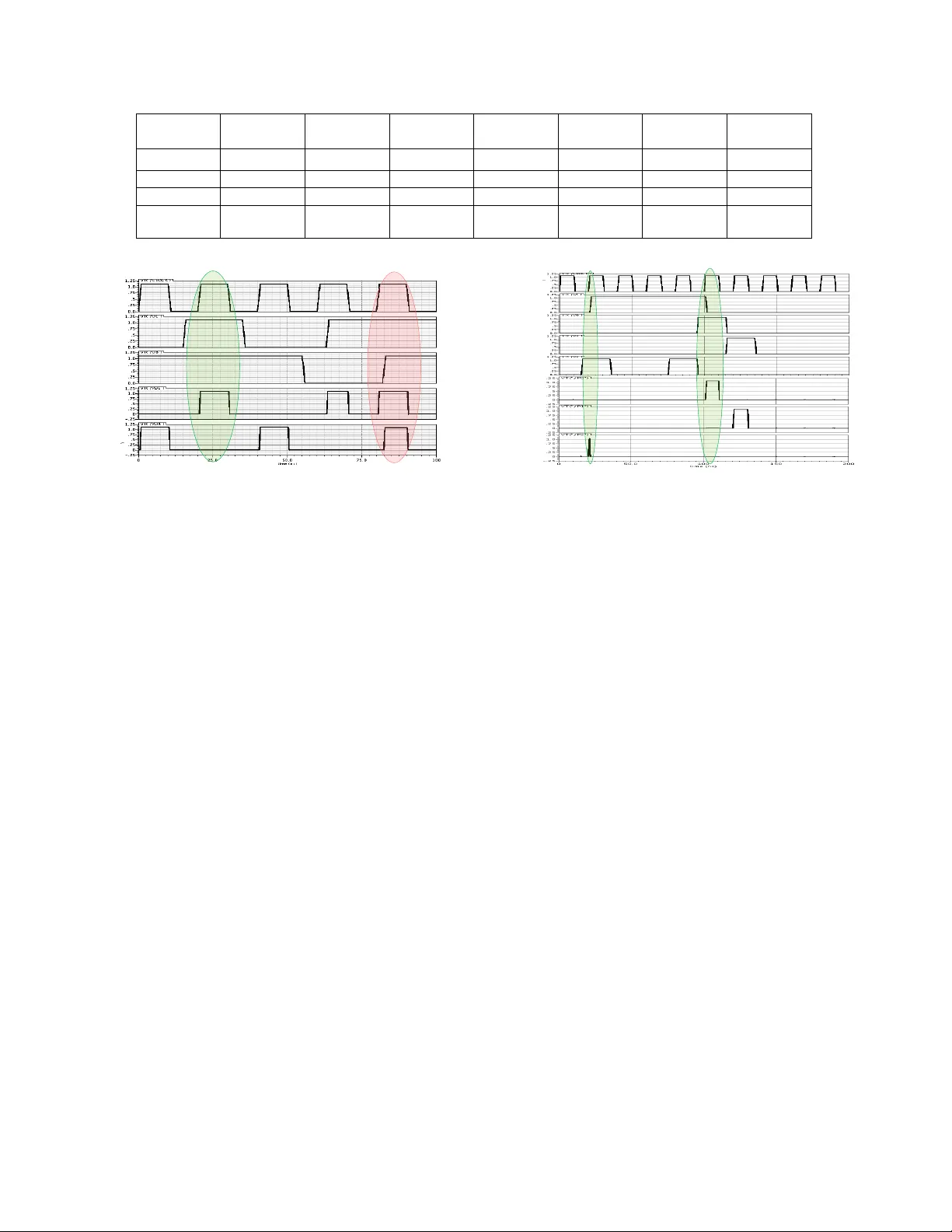

이러한 기존 설계들을 45 nm CMOS 공정(FreePDK)에서 동일한 환경으로 재구현·시뮬레이션함으로써, 전력(µW), 지연(ns), PDP(fJ), 트랜지스터 수를 객관적으로 비교하였다. 결과는 Wang·Huang 1 설계가 0.177 ns의 최단 지연을 보였지만 79.11 µW의 높은 전력 소모와 14 fJ의 PDP를 기록해 실용성에 한계가 있음을 보여준다. 반면, Mohanraj 설계는 3.189 µW 전력, 0.274 ns 지연, 0.874 fJ PDP로 전력·지연·면적 모두에서 우수했지만, 레이스 컨디션과 전하 공유가 발생할 수 있는 구조적 결함을 가지고 있다.

논문은 이러한 결함을 두 가지 주요 문제로 정리한다. 첫째, 레이스 컨디션은 룩어헤드 신호가 클럭 상승 후에 도착할 경우, 현재 단계가 이미 출력 HIGH를 생성한 뒤 신호가 뒤늦게 들어와도 출력이 즉시 LOW로 전환되지 않아 다중 HIGH가 발생한다. 이는 고차 인코더에서 오류 전파를 일으킨다. 둘째, 전하 공유는 동적 회로에서 출력 노드가 인접 NMOS 트랜지스터에 의해 전하가 흐르면서 논리 HIGH 레벨이 떨어져 플리핑하거나 논리 LOW와 HIGH가 혼재하는 현상이다. 두 문제 모두 기존 설계가 충분히 고려하지 않아 실제 시스템에서 신뢰성을 저해한다.

이를 해결하기 위해 저자는 3단계 룩어헤드 구조와 액티브‑로우 제어를 결합한 새로운 8‑bit PE를 제안한다. 첫 번째 레벨(la0‑la2)은 0‑3비트에 대한 즉시 활성화된 룩어헤드 신호를 제공하고, 두 번째 레벨(LA_inter)은 4‑7비트를 제어한다. 최종 레벨(LA)은 현재 8‑bit 매크로 셀이 전체 우선순위를 보유하고 있는지를 판단한다. 회로는 동적 프리차지 단계에서 모든 출력이 0으로 초기화되고, 평가 단계에서는 입력에 따라 단 하나의 출력만이 1로 충전된다. 만약 현재 단계가 우선순위를 잃었을 경우 LA와 LA_inter가 1이 되어 rs0‑rs7을 강제로 LOW로 끌어내어 이미 충전된 출력도 즉시 소거한다. 이 메커니즘은 레이스 컨디션을 완전히 차단한다. 또한, 각 출력은 두 개의 NMOS만을 통해 그라운드에 연결되므로 전하 공유 경로가 최소화되어 전압 플리핑이 발생하지 않는다.

시뮬레이션 결과, 제안된 PE는 평균 전력 6.879 µW, 최악 지연 0.278 ns, PDP 1.912 fJ를 달성했으며, 트랜지스터 수는 79개다. 전력·지연·면적 측면에서 기존 설계와 비교해 경쟁력을 유지하면서, 레이스와 전하 공유라는 두 가지 치명적 결함을 완전히 제거했다. 또한, LA 신호를 이용한 계층화 설계가 가능하도록 설계되어 16‑bit·32‑bit 등 고차 PE로 손쉽게 확장할 수 있다.

결론적으로, 본 논문은 기존 8‑bit CMOS PE 설계가 놓친 신뢰성·확장성 문제를 체계적으로 분석하고, 이를 해결하기 위한 구조적 혁신을 제시한다. 제안된 설계는 전력·지연·면적 모두에서 우수한 성능을 유지하면서, 레이스 컨디션과 전하 공유를 완전히 배제하고, 고차 인코더와의 연쇄 사용을 지원한다는 점에서 차세대 디지털 시스템에 적용 가능한 실용적인 우선순위 인코더 솔루션이라 할 수 있다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기