엑사스케일을 위한 다중코어 공동 설계 자동화와 맞춤형 워크로드 생성

초록

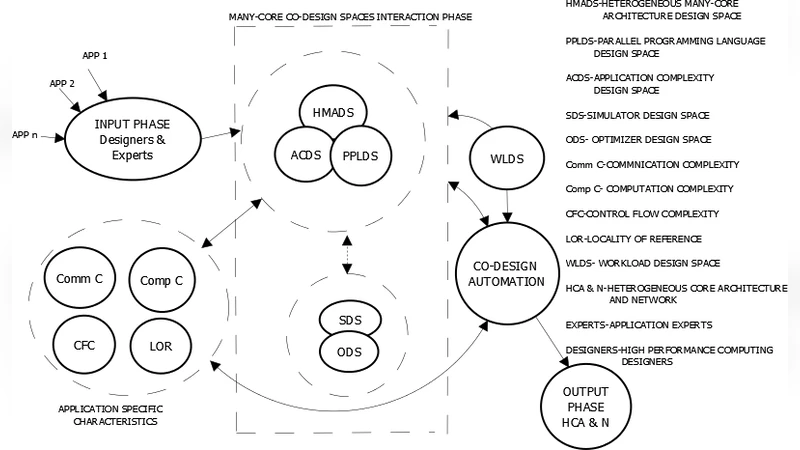

본 논문은 이기종 다중코어 시스템 설계를 위한 공동 설계 자동화 프레임워크를 제안한다. 설계 공간(응용, 아키텍처, 프로그래밍 모델, 시뮬레이터, 최적화)을 연계하고, 그래프 이론 기반의 사용자 정의 워크로드 생성기를 통해 계산·통신·제어 복잡도와 지역성 등을 정량화한다. 사례 연구와 시뮬레이션 결과를 통해 제안 기법의 효용을 입증한다.

상세 분석

이 논문은 엑사스케일 수준의 이기종 다중코어 시스템을 설계하기 위한 ‘공동 설계 자동화(co‑design automation)’라는 개념을 중심으로 전개된다. 먼저 응용 프로그램 복잡도 설계 공간, 하드웨어 아키텍처 설계 공간, 병렬 프로그래밍 모델 설계 공간, 시뮬레이터 설계 공간, 최적화 설계 공간 등 다섯 개의 설계 공간을 정의하고, 이들 사이의 상호 의존성을 파악한다. 저자는 이러한 의존성을 알고리즘 집합으로 모델링하고, 각 설계 공간의 소프트웨어 모듈과 연동시켜 전력·성능을 동시에 최적화하는 이기종 코어 구성을 자동으로 도출한다는 목표를 제시한다.

핵심 기여는 ‘맞춤형 워크로드 생성기(customizable workload generator)’이다. 사용자는 응용 복잡도 모델링 툴(ACM)을 통해 목표 응용 프로그램의 계산·통신 그래프를 추출하고, 이를 기반으로 그래프 이론 기반 워크로드 모델을 생성한다. 노드 가중치는 수치·반수치·비수치 알고리즘 및 일반 연산을 나타내며, 엣지 가중치는 데이터 전송량과 통신 빈도로 정의된다. 이러한 모델은 계산 복잡도(C1), 통신 복잡도(C2), 제어 흐름 복잡도(C3), 지역성(C4) 네 가지 매개변수를 확률 분포에 따라 조정할 수 있어, 다양한 시나리오의 ‘서지(surge)’를 인위적으로 만들 수 있다.

논문은 기존 벤치마크 스위트(SPEC, LINPACK, SPLASH‑2, PARSEC, Rodinia 등)의 한계를 지적한다. 기존 스위트는 정적인 커널 집합에 머물러 있어, 새로운 이기종 아키텍처의 특성을 충분히 드러내기 어렵다. 제안된 워크로드 모델은 이러한 한계를 극복하고, 응용 프로그램 클로닝(application cloning)까지 지원한다는 점에서 차별성을 갖는다.

하지만 구현 상세와 평가가 부족하다. 워크로드 생성 알고리즘(‘ALGOBANK’)의 구체적인 구조, 분포 파라미터 설정 방법, 그리고 생성된 워크로드가 실제 어플리케이션과 얼마나 유사한지를 정량적으로 보여주는 실험 결과가 거의 없다. 또한 시뮬레이터 ‘XYZ’에 대한 설명이 전혀 없으며, 시뮬레이션 설정, 워크로드 규모, 측정 지표(전력, CPI, 메모리 대역폭 등)의 구체적 수치가 제시되지 않는다. 따라서 제안 기법의 실효성을 검증하기 어렵다.

또한 논문 전반에 걸쳐 문장 구조가 비정형적이고, 오탈자와 중복 표현이 빈번해 가독성을 크게 저해한다. 설계 공간 간 인터페이스를 어떻게 구현하고, 자동화 흐름을 어떻게 스케줄링하는지에 대한 흐름도와 알고리즘 의사코드가 부재한 점도 아쉽다.

요약하면, 이 논문은 다중코어 공동 설계 자동화와 맞춤형 워크로드 생성이라는 흥미로운 연구 방향을 제시하지만, 구체적인 방법론과 실험적 검증이 부족해 현재 단계에서는 개념적 제안에 머무른다. 향후 연구에서는 알고리즘 구현 세부사항, 워크로드 생성의 통계적 타당성, 그리고 실제 하드웨어 프로토타입이나 상세 시뮬레이션을 통한 성능 평가가 필요하다.

댓글 및 학술 토론

Loading comments...

의견 남기기