고속 CIC 필터 기반 디시메이션 프로세스 향상

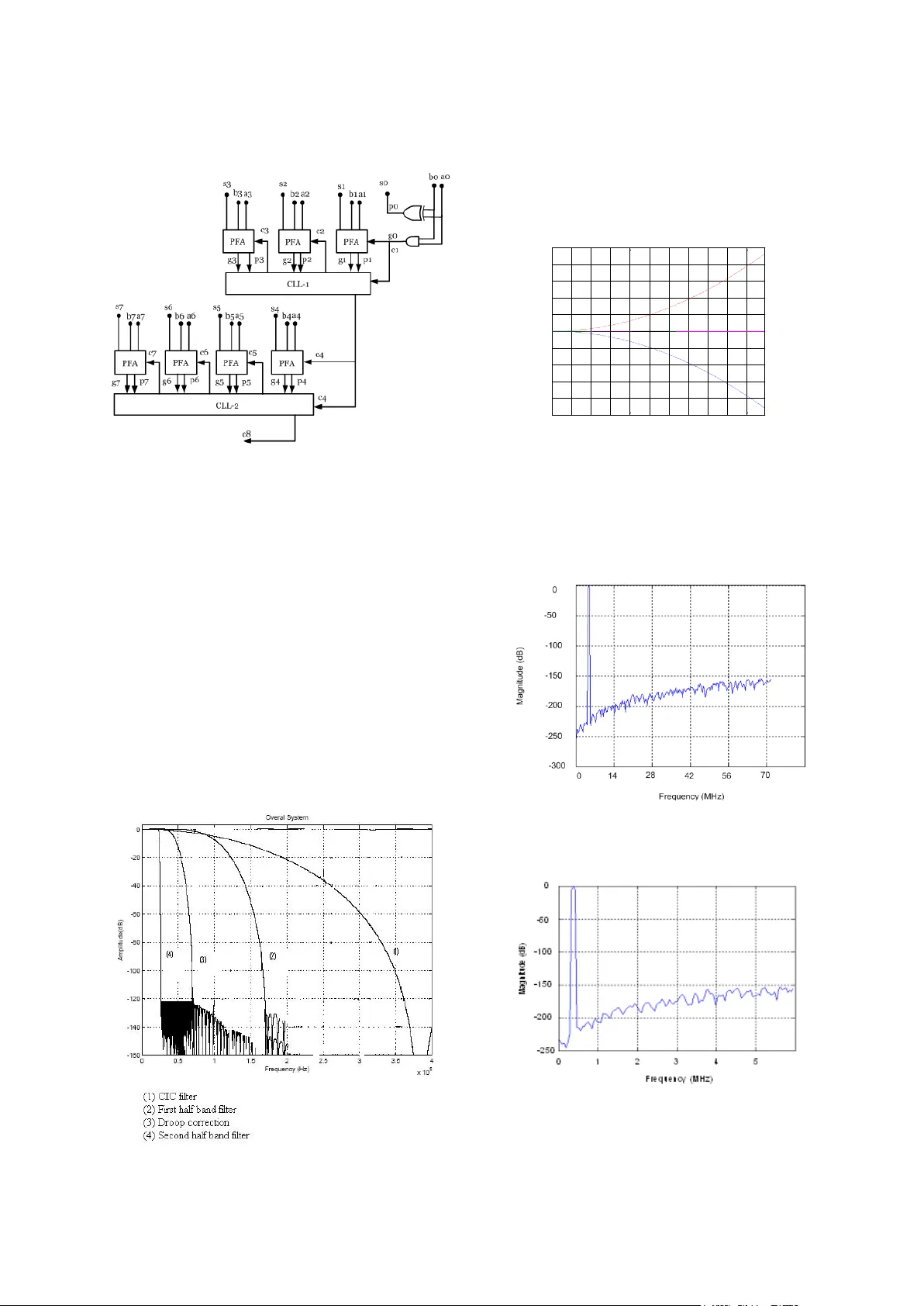

** 본 논문은 오버샘플링 ADC에서 사용되는 디시메이션 단계에 초점을 맞추어, 고속 Cascaded Integrator‑Comb (CIC) 필터와 그 주변 회로(하프밴드 필터, 드롭 보정 필터)를 VLSI 수준에서 구현한다. 트렁케이션, 파이프라인 구조, 수정된 캐리 룩어헤드 가산기(MCLA)를 적용해 연산 속도를 190 MHz까지 끌어올리고, 전력 소모는 0.18 µm CMOS 기준 3.5 mW로 제한하였다. 설계는 Verilog‑HDL…

저자: Rozita Teymourzadeh, Masuri Othman

**

본 연구는 오버샘플링 기반 아날로그‑디지털 변환기(ADC)에서 핵심적인 디시메이션 단계의 성능을 향상시키기 위해, Cascaded Integrator‑Comb(CIC) 필터와 그 주변 회로를 VLSI 수준에서 설계·구현하였다. 논문은 먼저 ΣΔ 변조기의 고속 샘플링 출력(예: 6.144 MHz)을 48 kHz의 Nyquist 레이트로 낮추는 전체 디시메이션 흐름을 제시한다. 이 흐름은 (1) 16배 디시메이션을 수행하는 CIC 필터, (2) 두 개의 하프밴드 필터, (3) 드롭 보정 필터 순으로 구성된다. CIC 필터는 N=5, M=1, R=16의 파라미터를 사용해 설계되었으며, 이때 내부 레지스터 폭은 최대 25 bit가 된다. 레지스터 폭 계산식은 max G = (RM)^N, max B = ⌈log₂

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기