와이드라 전류 미러와 멤리스터 통합 설계

초록

**

본 논문은 기본 BJT 전류 미러와 와이드라 전류 미러에 멤리스터를 삽입한 회로를 제안하고, 전력 소모, 전체 고조파 왜곡(THD), 칩 면적 측면에서 기존 와이드라 회로와 비교 분석한다. 시뮬레이션 결과 멤리스터 적용 시 칩 면적이 크게 감소하고 THD가 낮아지며, 전력 손실도 감소하는 경향을 보였지만, 사용된 Joglekar 멤리스터 모델의 이상성 때문에 전력 감소에 대한 확정적인 결론은 내리지 못한다.

**

상세 분석

**

이 논문은 세 가지 핵심 요소—기본 BJT 전류 미러, 와이드라 전류 미러, 그리고 멤리스터—를 차례로 소개한 뒤, 와이드라 회로에 멤리스터를 대체 소자로 삽입한 새로운 토폴로지를 제시한다. 기본 전류 미러는 두 개의 BJT와 입력 저항 하나로 구성되며, 입력 전류를 복제해 출력에 일정한 전류를 제공한다. 와이드라 변형은 출력 트랜지스터에 에미터 저항을 추가함으로써 높은 입력 전류 대비 낮은 출력 전류를 구현하고, 고저항(≥50 kΩ) 소자를 회로에 직접 배치하지 않아도 된다. 이는 집적 회로 설계 시 면적 절감과 제조 비용 감소에 크게 기여한다.

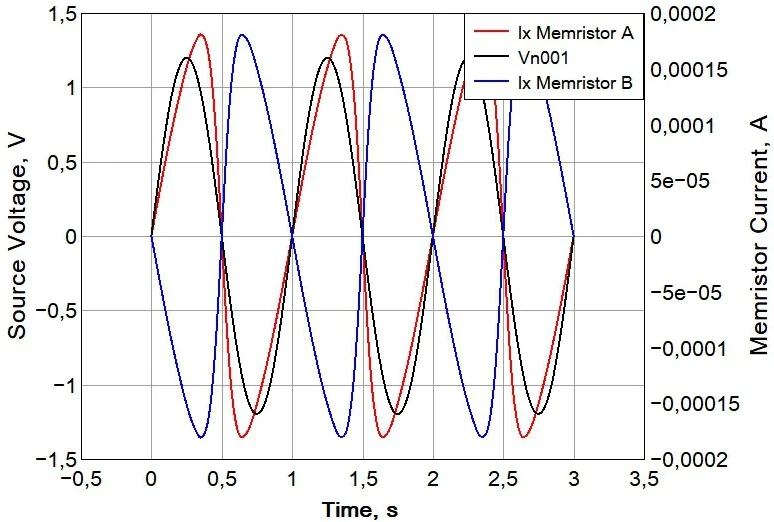

멤리스터는 전하와 플럭스 사이의 관계를 정의하는 네 번째 회로 소자로, 저항값이 과거 전류·전압 이력에 따라 비선형적으로 변한다. 논문에서는 Joglekar 모델을 LTspice에 구현해 입력·출력 저항 대신 사용하였다. 시뮬레이션 결과, 멤리스터를 적용한 와이드라 회로는 동일한 입력 전류·전압 조건에서 출력 전류 특성이 기존 회로와 거의 동일한 형태를 유지하면서도, 저항 대신 멤리스터가 차지하는 면적이 나노스케일 수준이므로 전체 칩 면적이 크게 감소한다는 점이 강조된다.

전력 분석에서는 저항 기반 회로가 입력 저항에서 약 56 mW, 출력 저항에서 수백 nW 수준의 손실을 보인 반면, 멤리스터 기반 회로는 입력 멤리스터에서 2.4 mW, 출력 멤리스터에서 0.77 µW 정도로 손실이 현저히 낮았다. 그러나 Joglekar 모델은 이상적인 비손실 소자를 가정하고 있어 실제 실리콘 기반 멤리스터의 온-저항, 스위칭 에너지, 누설 전류 등을 반영하지 않는다. 따라서 전력 절감 효과는 모델링 한계에 크게 좌우된다.

THD 측정에서는 기본 와이드라 회로의 THD가 약 1.94 %인 반면, 멤리스터 삽입 회로는 1.22 %로 감소하였다. 이는 멤리스터의 히스테리시스 특성이 고조파 성분을 억제하고, 전압·전류 파형을 보다 선형에 가깝게 만든 것으로 해석된다. 다만 시뮬레이션 샘플링 및 해석 조건이 동일하게 유지된 점을 고려하면, 실제 회로에서 온도·공정 변동에 따른 THD 변동은 추가 실험이 필요하다.

종합적으로, 논문은 멤리스터를 와이드라 전류 미러에 통합함으로써 면적 절감과 고조파 감소라는 두 가지 실용적 이점을 제시한다. 그러나 전력 효율에 관한 결론은 멤리스터 모델의 비현실성 때문에 불확실하며, 실험적 검증 및 보다 정교한 물리 모델링이 뒤따라야 한다는 한계점을 명확히 제시한다.

**

댓글 및 학술 토론

Loading comments...

의견 남기기