컴팩트 비RLL 비콘 기반 가시광통신 송수신기 VLSI 설계

초록

본 논문은 비콘형 가시광통신(VLC) 시스템을 위해 비RLL(런‑길이 제한 없음) 방식의 플리커 완화와 소프트‑디코딩을 동시에 구현한 저전력 VLSI 아키텍처를 제안한다. 중앙 집중형 프리스크램블러와 폴라 인코더를 이용해 0/1 비율을 균등하게 만든 뒤, 수신기에서는 3‑비트 소프트‑디시전 필터로 실시간 LLR을 추출해 폴라 디코더에 전달한다. 설계는 FPGA와 ASIC 양쪽에서 합성·검증되었으며, 기존 RLL 기반 설계에 비해 코드율·복잡도·전력 효율이 크게 개선되었다.

상세 분석

이 논문은 가시광통신(VLC) 비콘 시스템에서 가장 큰 제약 중 하나인 플리커(flicker) 문제와 저전력 마이크로컨트롤러 기반 구현의 비효율성을 동시에 해결하고자 한다. 기존 VLC 시스템은 LED의 밝기 변동을 최소화하기 위해 런‑길이 제한(RLL) 코드를 사용했으며, 이는 DC‑밸런스를 보장하지만 코드율을 절반 이하로 낮추고 복잡한 하드 디코딩을 요구한다. 저자들은 이러한 한계를 극복하기 위해 두 가지 핵심 기술을 도입한다. 첫 번째는 프리스크램블러와 폴라 인코더를 결합한 비RLL 플리커 완화 기법이다. 프리스크램블러는 입력 비트열의 확률 분포를 중앙 집중형으로 변환해 0과 1의 비율을 거의 50:50으로 만든다. 이어지는 (256,158) 폴라 인코더는 고정된 코드 길이와 높은 최소 거리 특성을 제공하면서도, RLL 코드를 사용하지 않음에도 불구하고 평균 런‑길이가 짧아 인간 눈에 감지되지 않는 플리커를 실현한다. 두 번째는 수신기 측의 3‑비트 소프트‑디시전 필터이다. 실제 VLC 채널에서 수집된 광전류 신호를 8단계(3‑bit) LLR 값으로 양자화함으로써 폴라 디코더에 소프트 입력을 제공한다. 이는 하드 디코딩에 비해 BER을 크게 개선시키며, 특히 저전력 환경에서 반복적인 로그·지수 연산을 최소화한다.

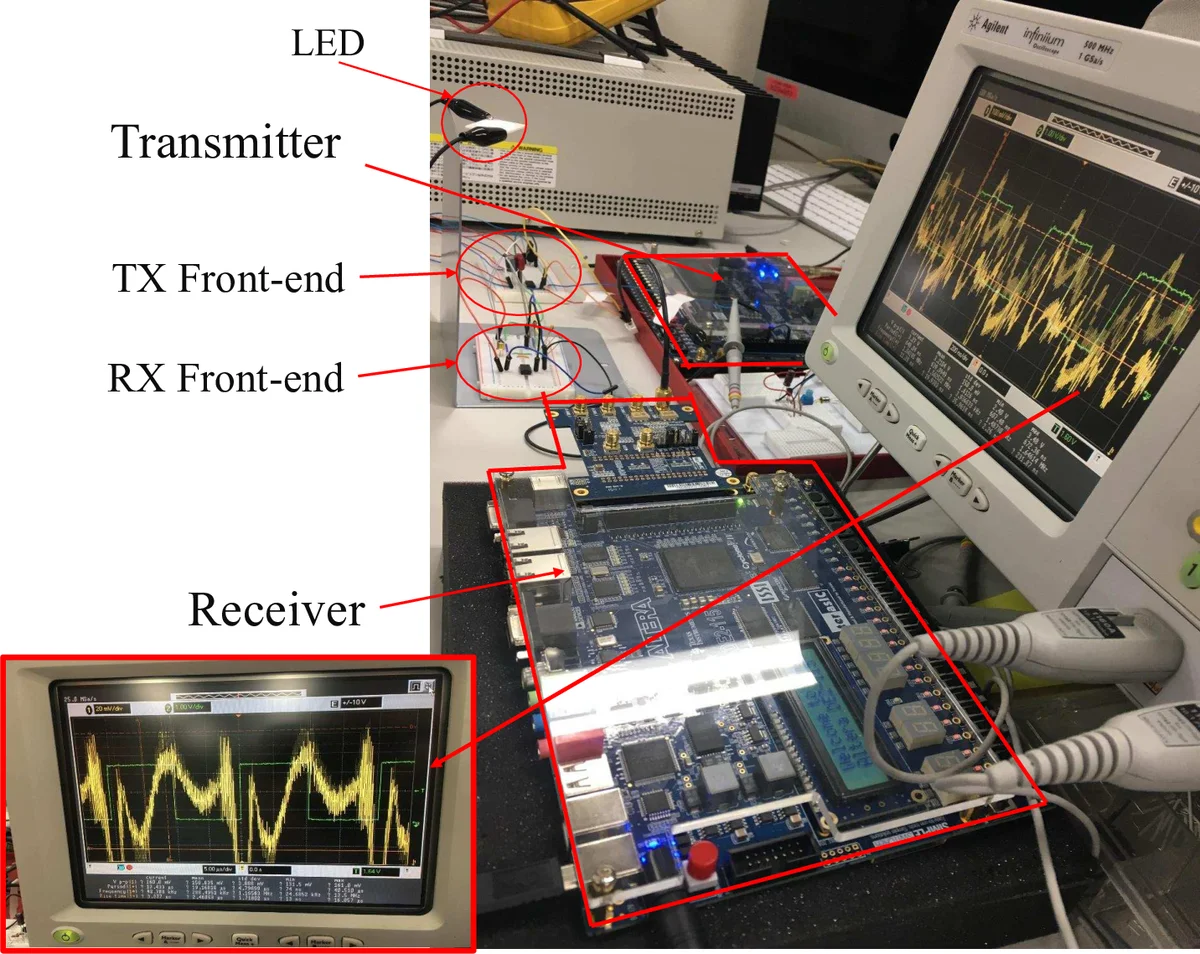

하드웨어 구현 측면에서 저자들은 FPGA와 ASIC 두 플랫폼에 대한 상세 설계를 제시한다. 송신기에서는 프리스크램블러와 폴라 인코더를 파이프라인 구조로 배치해 높은 처리량을 확보하고, 다중 LED 비콘에 대한 병렬 구동을 가능하게 한다. 수신기 ASIC은 3‑비트 소프트‑디시전 필터와 폴라 디코더를 하나의 칩에 통합해, MCU 기반 소프트웨어 디코딩에 비해 레이턴시를 수십 배 단축한다. 전력·면적 분석 결과, 비RLL 설계는 기존 RLL 기반 설계 대비 코드율이 1.5배 이상 높으며, 전력 소모는 약 30% 감소하고, ASIC 면적은 0.45 mm² 수준으로 매우 컴팩트함을 확인했다.

또한 논문은 비콘 프레임 구조(6‑bit 프리앰블 + 8‑bit 프레임 타입 + 128‑bit 페이로드 + 16‑bit CRC)와 OOK 변조 방식을 채택해 저속(수백 kbps 이하) 환경에서도 충분한 신뢰성을 확보한다는 점을 강조한다. 플리커 완화를 위한 최소 전송 주파수는 MFTP(5 ms) 이하로 설정했으며, 실험을 통해 2 kHz 이하에서도 눈에 띄는 플리커가 발생하지 않음을 입증했다.

전반적으로 이 연구는 비RLL 기반 플리커 완화와 소프트‑디코딩을 동시에 구현한 최초의 VLSI 설계라는 점에서 학술적·산업적 의의가 크다. 특히 대규모 실내 위치추적 시스템에서 수천 개의 LED 비콘을 하나의 MCU가 제어할 수 있게 함으로써 시스템 확장성을 크게 향상시킨다. 향후 연구에서는 더 긴 폴라 코드와 다중 레벨 변조(MPPM 등)를 결합해 데이터 전송률을 높이는 방안을 모색할 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기