대용량 리스트 사이즈를 위한 폴라 코드 리스트 연속 캔슬레이션 디코더 구현

초록

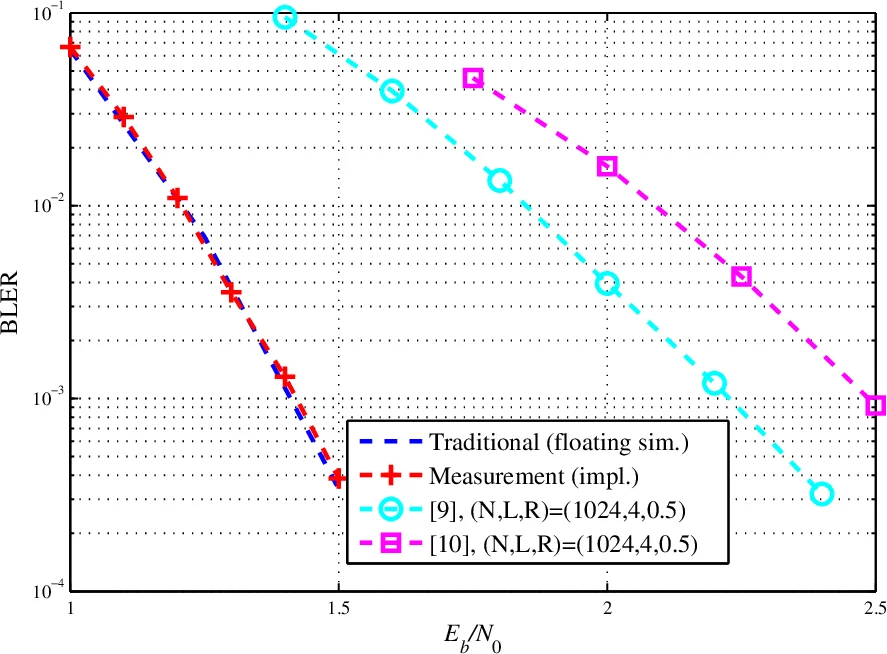

본 논문은 리스트 크기 L=32인 리스트 연속 캔슬레이션 디코더(LSCD)를 FPGA에 효율적으로 구현하기 위한 두 가지 저복잡도 설계 방안을 제시한다. 병렬‑F 직렬‑G 연산 구조와 선택적 확장 기반 리스트 관리(LCLM) 기법을 도입해 교차바 및 정렬기 복잡도를 크게 감소시켰으며, Altera Stratix V FPGA에서 4096‑비트 폴라 코드를 150 µs 내에 디코딩해 27 Mbps의 처리량을 달성하였다.

상세 분석

이 논문은 폴라 코드의 LSCD 구현이 리스트 크기 L에 따라 O(L²) 수준의 교차바와 정렬기 자원 소모로 급격히 복잡해지는 문제를 정확히 짚어낸다. 기존 설계는 L≤8 정도에서만 실용적이었으며, L=32와 같은 대용량 리스트를 지원하려면 FPGA 자원의 한계에 부딪힌다. 저자는 두 가지 핵심 아이디어로 이를 해결한다. 첫 번째는 “Parallel‑F Serial‑G”(PFSG) 연산 구조이다. F‑노드 연산은 모든 리스트 경로에 대해 동시에 수행할 수 있어 교차바가 필요 없으며, G‑노드 연산만을 직렬로 처리함으로써 전체 지연을 약 L/2 로 감소시킨다. 이때 메모리와 연산 유닛을 1:1 매핑하고, 사용되지 않는 메모리 블록을 β‑축소(Lβ) 방식으로 줄여 RAM 사용 효율을 높였다. 두 번째는 “Low‑Complexity List Management”(LCLM) 기법이다. 기존의 다중‑비트 디코딩(MBD)에서는 2^M 개의 경로가 확장돼 정렬 비용이 폭증하지만, LCLM은 신뢰도가 낮은 비트 집합 Au와 높은 비트 집합 Ar을 구분해 Au에 대해서만 완전 확장을 수행하고, Ar에 대해서는 최소 비용 선택을 통해 경로 수를 크게 억제한다. 이 과정에서 SE(Selective Expansion)와 MBD를 결합해, 확장 경로 수를 2^Mu·L 로 제한하면서도 오류 성능은 SE보다 우수함을 이론적으로 증명한다(γLCLM ≤ γSE). 하드웨어 설계에서는 PFSG와 LCLM을 통합한 모듈을 구현하고, 라디얼‑2L 병렬 정렬기를 사용해 정렬 지연을 최소화하였다. 결과적으로 전체 LSCD는 107 MHz 클럭에서 16019 사이클(≈149.7 µs)의 지연을 보이며, ALM 사용률 28.6%, RAM 사용률 43.8%로 기존 설계 대비 자원 효율이 크게 개선되었다. 블록 오류율(BLER) 실험에서도 부동소수점 기준 LSCD와 0.05 dB 이내의 성능 차이만을 보이며, 실제 FPGA 환경에서도 설계 목표를 충족한다.

댓글 및 학술 토론

Loading comments...

의견 남기기