대규모 MIMO용 고효율 소프트 출력 가우스‑시델 검출기

초록

본 논문은 대규모 MIMO 시스템에서 MMSE 검출의 복잡성을 피하기 위해 가우스‑시델(GS) 반복법을 기반으로 한 소프트‑출력 데이터 검출기를 제안한다. 2‑항 Neumann 급수를 이용한 초기값을 도입해 수렴 속도를 크게 향상시키고, VLSI 수준에서 여러 최적화를 적용해 처리 지연과 면적을 최소화하였다. 128×8 안테나 구성의 FPGA 구현 결과, 732 Mb/s의 처리량을 달성하면서 MMSE에 근접한 BER 성능을 보였다.

상세 분석

이 논문은 대규모 MIMO(다중 입력 다중 출력) 시스템에서 전통적인 최소 평균 제곱오차(MMSE) 검출이 요구하는 대규모 행렬 역연산의 O(N³) 복잡도를 회피하고자, 가우스‑시델(Gauss‑Seidel, GS) 반복법을 활용한 소프트‑출력 검출 알고리즘을 설계하였다. 핵심 아이디어는 정규화된 Gram 행렬 W가 대규모 안테나 환경에서 대각 우세(diagonally dominant)하고, 따라서 Hermitian 양정(positive‑definite) 특성을 갖는다는 점을 이용해 GS의 수렴성을 보장한다. 기존 GS 기반 검출기들은 초기값을 0 벡터로 설정해 수렴에 많은 반복이 필요했으나, 저자들은 2‑항 Neumann 급수(NSE) 근사를 이용해 W⁻¹≈W⁻¹₂ = D⁻¹ – D⁻¹ E D⁻¹ (여기서 D는 대각, E는 비대각 성분) 를 계산하고, 이를 y_MF와 곱해 초기 추정값 s(0)를 얻는다. 이 초기값은 실제 MMSE 해에 매우 근접하므로, 전체 GS 반복 횟수 K를 크게 줄일 수 있다.

알고리즘 흐름은 크게 네 단계로 나뉜다. ① 전처리 단계에서 W와 매치드‑필터 출력 y_MF를 계산하고, W를 D+L+Lᴴ 형태로 분해한다. ② 위의 2‑항 NSE를 이용해 초기값 s(0)를 구한다. ③ GS 반복식 s(k) = (D+L)⁻¹ (y_MF – Lᴴ s(k‑1)) 를 K번 수행한다. ④ 최종 추정값을 이용해 효율적인 LLR(로그우도비) 계산을 수행한다. 여기서 LLR 계산에 필요한 채널 이득 μ_i는 W⁻¹ 대신 W⁻¹₂의 대각 원소를 사용해 근사함으로써 추가적인 행렬 역연산을 회피한다.

복잡도 분석 결과, 전체 연산량은 O((K+2) N_t²) 복소수 곱셈으로, K가 2~3 정도이면 기존 NSE(K≥2) 혹은 Cholesky/QR 기반 MMSE 대비 5배 이상 연산량을 절감한다. 또한, FPGA 구현에서는 파이프라인화된 전처리 유닛(PU), GS 연산 유닛(GSMU), 초기값 계산 유닛(ISCU), SINR 계산 유닛(SCU), LLR 계산 유닛(LCU) 등으로 모듈화하여 각 단계의 지연을 최소화하고, 메모리 접근을 효율적으로 설계하였다.

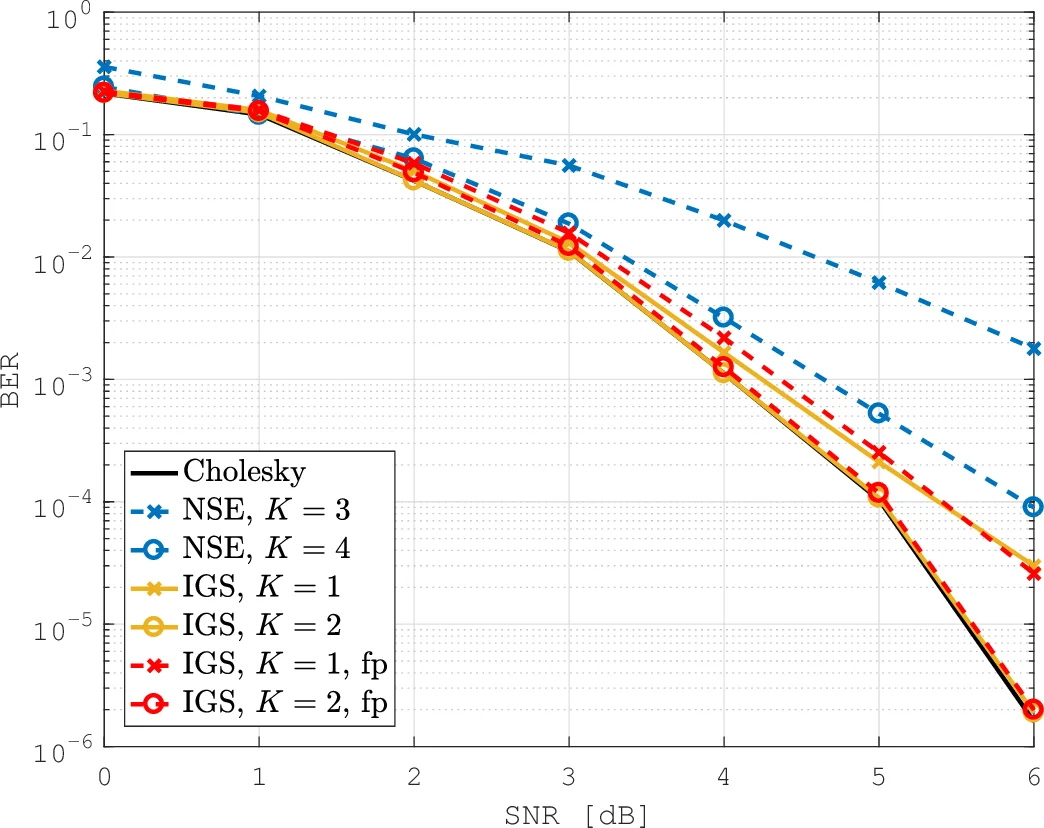

시뮬레이션에서는 64‑QAM, 1/2 rate 컨볼루션 코드를 사용해 BER을 평가했으며, 안테나 수(N_r=128, N_t=8)와 부하 팩터가 높은 경우에도 제안된 IGS(Improved GS) 검출기가 기존 NSE 기반 검출기와 전통적인 GS 검출기보다 0.5~1 dB 정도의 SNR 이득을 보였다. 상관 채널(ζ_r=0.4)에서도 성능 저하가 미미했으며, 이는 초기값이 채널 경도에 강인함을 의미한다. 최종적으로 Xilinx Virtex‑7 XC7VX690T FPGA에 구현된 설계는 732 Mb/s 처리량을 달성하면서, 면적과 전력 효율 면에서 기존 설계보다 우수함을 입증하였다.

이 연구는 대규모 MIMO 시스템에서 실시간 고속 소프트‑출력 검출을 구현하기 위한 실용적인 설계 지침을 제공한다. 특히, 초기값을 NSE로 빠르게 얻는 전략과 하드웨어 친화적인 GS 반복 구조는 차세대 5G·6G 베이스스테이션 및 massive IoT 환경에서 요구되는 저지연·저전력 요구사항을 충족시키는 데 큰 의미가 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기