3비트 상수진폭 프리코더 VLSI 설계로 Massive MU‑MIMO 효율 극대화

본 논문은 8단계(3‑bit) 상수진폭(CM) 송신기를 이용한 Massive MU‑MIMO 다운링크용 비선형 프리코딩 알고리즘을 제안하고, 이를 고속 매트릭스‑벡터 곱 엔진 기반 VLSI 아키텍처로 구현한다. Xilinx Virtex‑7 FPGA에서 구현한 결과, 기존 2‑bit(두 개의 1‑bit DAC) 설계 대비 최대 3.75 dB의 전송 전력 절감과 2.7배 이하의 자원 증가만을 보이며, BER 성능에서도 현저히 우수함을 입증한다.

저자: Oscar Casta~neda, Sven Jacobsson, Giuseppe Durisi

본 논문은 5세대(5G) 이동통신 시스템에서 핵심 기술로 떠오르고 있는 Massive Multi‑User MIMO(MU‑MIMO) 기술의 하드웨어 구현 문제를 해결하고자 한다. 기존의 Massive MU‑MIMO 베이스스테이션은 수백 개의 안테나와 RF 체인을 필요로 하며, 고정밀 디지털‑아날로그 변환기(DAC)를 사용하면 비용과 전력 소모가 급격히 증가한다. 이를 극복하기 위해 저정밀 DAC를 활용한 CM(상수진폭) 전송 방식을 도입하고, 이에 맞는 비선형 프리코딩 알고리즘과 VLSI 구현을 제안한다.

1. **시스템 모델 및 문제 정의**

- 베이스스테이션은 B개의 안테나를 가지고 U(≤B)개의 단일 안테나 사용자에게 동시에 데이터를 전송한다. 채널 행렬 H∈ℂ^{U×B}가 알려져 있다고 가정한다.

- 전송 신호 x는 CM 알파벳 X={e^{j2πp/P}, p=0,…,P−1}에 속해야 하며, 여기서 P는 위상 수, 즉 비트 수에 해당한다. 본 연구에서는 P=8(3‑bit) CM을 사용한다.

- 목표는 평균제곱오차(MSE)를 최소화하는 비선형 프리코딩 문제(OPP)를 근사해 해결하는 것이다.

2. **C3PO 알고리즘 설계**

- 고신호대비(SNR) 가정(N₀→0) 하에 OPP를 간단히 min_{x∈X^B,α∈ℂ}‖αs−Hx‖² 형태로 변형한다.

- α는 닫힌 형태 α̂ = (sᵀ H H x)/(‖s‖²) 로 구하고, 이를 대입하면 ‖A x‖² 최소화 문제(OPP**)가 된다. 여기서 A = QH, Q = I_U − ssᵀ/‖s‖².

- x∈X^B 제약을 완화해 8‑phase CM 알파벳을 둘러싼 정팔각형 볼록다각형 B 로 확장한다. 다만, 이 완화만으로는 해가 0벡터가 되므로 ‖x‖²에 대한 음의 정규화 항(−δ‖x‖²)을 추가해 해가 다각형 경계에 머물게 만든다.

- 최종 목표 함수는 f(x)=½‖A x‖² − (δ/2)‖x‖² 로 정의하고, 이를 전방‑후방 분할(FBS) 방식으로 반복 최적화한다.

- FBS 단계는 (i) gradient step: z^{t+1}=x^{t}−τ Aᴴ A x^{t} (여기서 τ는 고정 스텝 사이즈)와 (ii) proximal step: x^{t+1}=prox_{g}(z^{t+1}) 로 구성된다.

- proximal 연산은 각 복소수 요소를 정팔각형 B 로 투사하는 작업이며, 6개의 영역(A–F) 판별을 통해 가장 가까운 경계점 혹은 꼭짓점으로 매핑한다. 라인 방정식(`1`~`6`)을 이용해 비교 연산만으로 구현한다.

3. **VLSI 아키텍처**

- 기존 2‑bit C2PO 설계를 기반으로 하되, B/U개의 선형 배열(linear array)과 각 배열당 U+1개의 프로세싱 엘리먼트(PE)를 배치한다.

- 각 PE는 (i) H 행렬의 해당 행을 저장하는 메모리, (ii) 복소수 MAC 유닛, (iii) 위에서 설명한 프로젝션 유닛을 포함한다.

- 행렬‑벡터 곱은 Cannon’s 알고리즘을 적용해 두 단계로 나누어 수행한다. 첫 단계에서 τx^{t}를 순환 교환해 w=H(τx^{t})를 계산하고, 두 번째 단계에서 w를 다시 순환 교환해 z^{t+1}=x^{t}−H_Υ w를 얻는다.

- 한 반복당 필요한 클럭 수는 2U+log₂(B/U)+9 사이클이며, 파이프라인 구조 덕분에 높은 처리량을 유지한다.

- 정밀도는 입력/출력 14‑bit(8‑fraction), H 행렬 11‑bit(8‑fraction), MAC 연산은 18‑bit(15‑fraction) 등으로 설계해 양자화 손실을 최소화한다. 프로젝션 유닛은 상수값을 4~5‑bit 정수로 표현해 곱셈을 배제하고, 30개의 가산·뺄셈 연산만으로 구현한다.

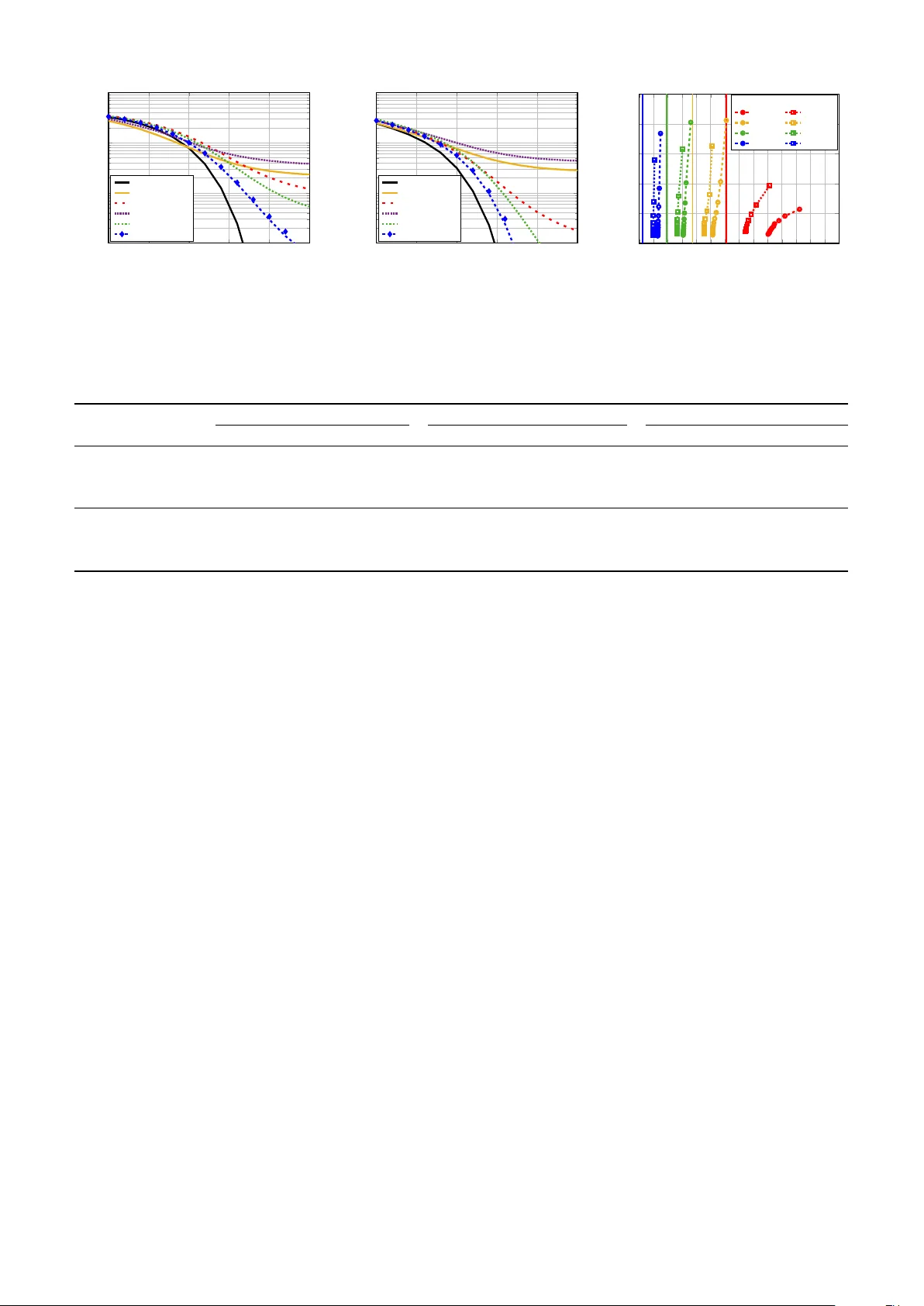

4. **시뮬레이션 및 FPGA 구현 결과**

- 시뮬레이션은 B=32,64,128,256, U=16, BPSK 및 16‑QAM 환경에서 10,000 Monte‑Carlo 시행을 통해 BER을 평가했다. C3PO는 t_max=9 반복에서 C2PO 대비 1% BER 기준 전송 전력 이득을 B=32, BPSK에서 3.75 dB, B=256, 16‑QAM에서 1.75 dB 제공한다.

- 구현은 Xilinx Virtex‑7 XC7VX690T FPGA에 Verilog로 합성했으며, 리소스 사용량(LUT, Slice, DSP48)은 B가 증가함에 따라 거의 선형적으로 증가한다. 예를 들어 B=256일 때 C3PO는 224 k LUT, 101 k FF, 1 088 DSP48을 사용한다.

- 최대 클럭 주파수는 400 MHz 이하이며, 처리량은 300 Msymbol/s 수준이다. 전력 소모는 0.79 W(32‑antenna)에서 10 W(256‑antenna)까지 B에 비례한다.

- 전체적으로 C3PO는 기존 2‑bit 설계 대비 2.7배 이하의 FPGA 자원 증가와 3.75 dB 전송 전력 절감이라는 두 마리 토끼를 잡았다.

5. **결론 및 의의**

- 3‑bit CM 프리코더는 하드웨어 비용·전력 효율·성능 측면에서 2‑bit(두 개의 1‑bit DAC) 설계보다 현저히 우수함을 입증한다.

- 제안된 VLSI 아키텍처는 고속 매트릭스‑벡터 곱과 저복잡도 프로젝션을 결합해 대규모 Massive MU‑MIMO 시스템에 실시간 적용 가능하도록 설계되었다.

- 향후 연구에서는 더 높은 비트 수(예: 4‑bit)와 다중셀 환경, 그리고 실제 RF 테스트보드와의 연동을 통해 시스템 수준의 에너지 효율을 검증할 필요가 있다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기