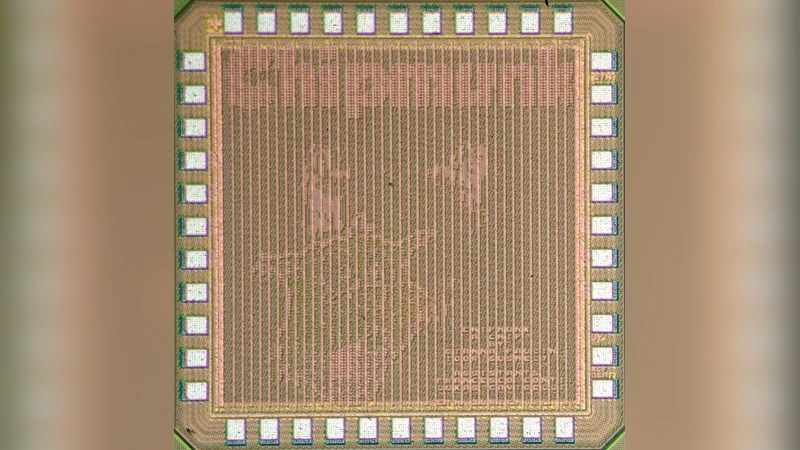

초소형 고효율 RNN 가속기 Chipmunk 0.9제곱밀리미터에 3.08Gop퍼와트 구현

초록

Chipmunk은 65 nm 공정으로 구현된 0.9 mm² 크기의 LSTM 전용 하드웨어 엔진이다. 1.24 mW 전력에서 32 Gop/s, 0.75 V에서 3.08 Gop/s/mW의 최고 에너지 효율을 달성한다. 다수의 엔진을 3×3·5×5 등으로 배열해 systolic 구조를 만들면 75타일 구성으로 실시간 음소 추출을 13 mW 이하의 평균 전력으로 수행한다.

상세 분석

Chipmunk 설계는 LSTM 연산을 세 가지 기본 연산(행렬‑벡터 곱, 원소‑원소 곱, 비선형 함수)으로 추상화하고, 이를 전용 데이터패스로 구현한 점이 핵심이다. 각 타일은 N lstm = 96개의 병렬 LSTM 유닛을 포함하며, 유닛당 8‑bit 고정소수점 저장소와 16‑bit MAC 회로를 갖춘다. 가중치는 81.7 kB SRAM에 온‑칩에 배치해 메모리 대역폭 병목을 최소화했으며, 이는 기존 FPGA 기반 가속기 대비 수십 배 이상의 에너지 효율을 가능하게 한다.

행렬‑벡터 곱은 외부에서 입력되는 xₜ와 hₜ 벡터를 모든 유닛에 동시에 브로드캐스트하고, 내부에서 열 루프를 순차적으로 수행함으로써 파이프라인 효율을 극대화한다. 비선형 함수는 LUT 기반으로 구현돼 8‑bit 입력에 대해 빠른 룩업을 제공한다. 이러한 구조는 연산당 2 OP(곱+덧셈)으로 계산해 Gop/s 단위 성능을 산출한다.

스케일링 측면에서 Chipmunk은 타일 간에 수평·수직 데이터 흐름을 정의한 systolic 배열을 제안한다. 입력 벡터는 열 방향으로 전파되고, 각 행은 부분 행렬‑벡터 곱 결과를 누적해 다음 열에 전달한다. 마지막 열에서는 최종 hₜ를 생성해 다시 열 전체에 재전송한다. 이 방식은 가중치를 각 타일에 분산 저장하고, 중간 결과만 교환함으로써 메모리 요구량을 크게 줄인다. 75타일(예: 3×5×5) 구성에서는 0.09 ms 이하의 레이턴시로 10 ms 프레임 간격을 만족하며, 평균 전력은 12.5 mW 수준에 머문다.

전력·성능 면에서 Chipmunk은 동일 공정의 DNPU와 비교해 39 % 높은 에너지 효율을 보이며, 28 nm TPU 대비 면적 효율은 2.8배 우수하다. 또한 8‑bit 정밀도와 16‑bit MAC을 사용해 양자화 손실을 최소화하면서도 높은 정확도를 유지한다. 실리콘 측정 결과는 0.75 V에서 20 MHz, 1.24 V에서 168 MHz까지 동작 가능하며, 전압에 따라 전력은 1.2 mW~29 mW 범위이다.

요약하면, Chipmunk은 초소형 면적에 고정밀도 LSTM 연산을 온‑칩 메모리와 결합해 구현함으로써, 웨어러블·모바일 디바이스 수준의 실시간 음성 인식에 필요한 연산량을 전력 10 mW 이하로 처리할 수 있는 실용적인 솔루션을 제공한다.

댓글 및 학술 토론

Loading comments...

의견 남기기